MADHYA PRADESH BHOJ(OPEN) UNIVERSITY BHOPAL

# MCA-101

## COURSE INTRODUCTION

This course is designed for the learners who are beginners in the field of computer architecture. This is the age of digital technology. In this age it is very important to have some idea about digital techniques used in computer system. After going through this course learners will be able to understand the different number systems like binary, octal, decimal and hexadecimal. Different types of gates, basic memory circuits, combinational and sequential circuits are discussed in this course.

There are two blocks in this course.

Block 1 deals with the basic concept of number system, data representation, logic gates and logic family. After going through this block learners will be comfortable to learn block 2.Block 2 concentrates on basic principles of combinational and sequential circuits. At the end of this block learners will have a clear concept of register, counter and memory organization.

Each unit of these blocks includes some along-side boxes to help you know some of the difficult, unseen terms. Some "EXERCISES" have been included to help you apply your own thoughts. You may find some boxes marked with: "LET US KNOW". These boxes will provide you with some interesting and relevant additional information. Again, you will get "CHECK YOUR PROGRESS" questions. These have been designed to self-check your progress of study. It will be helpful for you if you solve the problems put in these boxes immediately after you go through the sections of the units and then match your answers with "ANSWERS TO CHECK YOUR PROGRESS" given at the end of each unit.

## **BLOCK INTRODUCTION**

This course contains fifteen units in two blocks. **Block I** contains 8 units. These units discuss the basic concept of digital logic. Unit 1 deals with the basic concept of different number systems and their conversion. Unit 2 introduces binary arithmetic like r's and (r-1)'s complement etc. The basic of data representation like fixed point and floating point are discussed in Unit 3. Introduction to code conversion techniques like Gray code, BCD, Excess - 3 are discussed in unit 4. Unit 5 discusses the introduction of boolean algebra and their properties, De - Morgan's theorem etc. The concept of logic gates like AND, OR, NAND,NOR, XOR etc. are discussed in unit 6. Unit 7 discusses the details of floating point number representation. Logic family and their properties are discussed in unit 8.

## MASTER OF COMPUTER APPLICATION / MASTER OF SCIENCE IN INFORMATION TECHNOLOGY

## **Digital Techniques**

| DETAILED SYLLABUS                                                                                                                                                                                                                                                                               |                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| BLOCK-1<br>Semester I                                                                                                                                                                                                                                                                           |                    |

| F                                                                                                                                                                                                                                                                                               | Page No.           |

| Unit 1: Introduction to Number Systems [5 marks]<br>Decimal, Binary, Hexadecimal and Octal number system, Number system conversion                                                                                                                                                              | <b>7-18</b><br>ons |

| <b>Unit 2: Binary Arithmetic [6 marks]</b><br>Complement: r's and (r-1)'s complement, Binary addition, Binary subtraction, Binary multiplication, Binary division.                                                                                                                              | 19-30              |

| Unit 3: Introduction to Data Representation [6 marks]<br>Fixed Point representation and Floating point representation                                                                                                                                                                           | 31-38              |

| Unit 4: Code Conversion [5 marks]<br>Gray code, BCD, ASCII, EBCDIC, Conversion from Binary to Gray and Vice-versa                                                                                                                                                                               | 39-46              |

| Unit 5: Boolean Algebra [5 marks]<br>Introduction, Properties, De-Morgan's Theorem, Duality Principle                                                                                                                                                                                           | 47-55              |

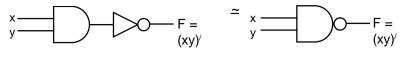

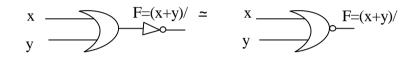

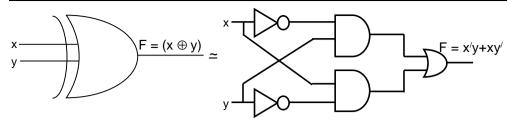

| Unit 6: Logic Gates [5 marks]<br>Logic Gates: AND, OR, NOT, NAND, NOR, XOR; Conversion of the logic gates                                                                                                                                                                                       | 56-75              |

| <b>Unit 7: Floating Point Number Representation [5 marks]</b><br>Floating point number, Normalization of floating point, overflow and underflow, detection of overflow, IEEE floating point standard                                                                                            | 76-94              |

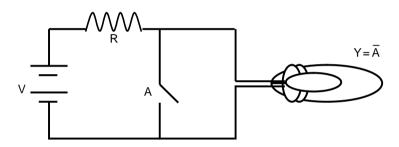

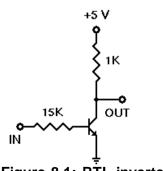

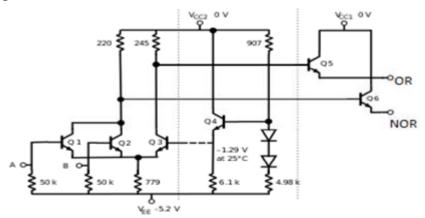

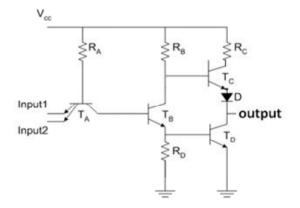

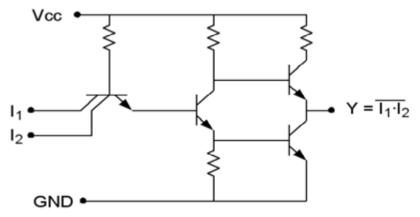

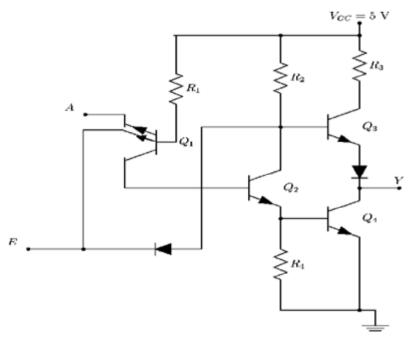

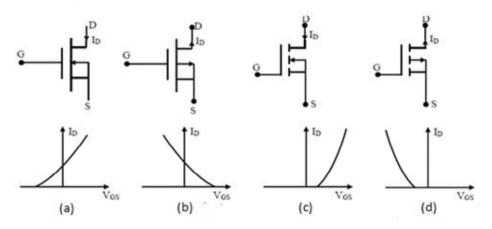

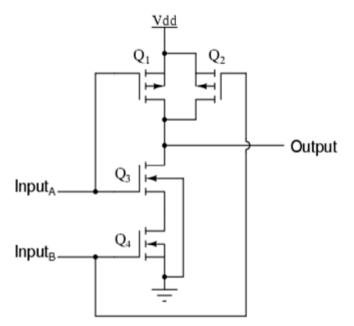

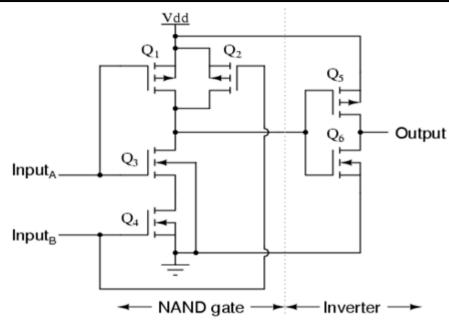

| <b>Unit 8: Logic Families [6 marks]</b><br>Introduction, Registror Transistor Logic(RTL), Integrated Injection logic(IIL),<br>Diode- Transistor Logic(DTL), Emitter-Coupled Logic(ECL), Transistor- Transistor<br>Logic(TTL), TTL-NAND, Tri State Logic, MOS devices, Logic gates with MOSFET's | 95-112             |

\*\*\*\*\*

## **UNIT 1 : INTRODUCTION TO NUMBER SYSTEMS**

## UNIT STRUCTURE

- 1.1 Learning Objectives

- 1.2 Introduction

- 1.3 Number System

- 1.3.1 Decimal Number System

- 1.3.2 Binary Number System

- 1.3.3 Octal Number System

- 1.3.4 Hexadecimal Number System

- 1.4 Number System Conversion

- 1.4.1 Binary to Decimal Conversion

- 1.4.2 Decimal to Binary Conversion

- 1.4.3 Octal to Decimal Conversion

- 1.4.4 Decimal to Octal Conversion

- 1.4.5 Hexadecimal to decimal Conversion

- 1.4.6 Decimal to Hexadecimal Conversion

- 1.5 Let Us Sum Up

- 1.6 Further Reading

- 1.7 Answers to Check Your Progress

- 1.8 Model Questions

## 1.1 LEARNING OBJECTIVES

After going through this unit, you will be able to :

- I define and describe number systems like decimal, binary, octal, and hexadecimal.

- I convert from one number system to another number system.

## 1.2 INTRODUCTION

Computer system uses different number systems to represent data.

In this unit, we will be able to understand how numbers are represented in different number systems.

In this unit, we will learn about decimal, binary, octal and hexadecimal number systems. In addition to this, we will also discuss the ways for converting from one number system to one another number system. Once, we have the knowledge of number systems, then in the next units, we will discuss about binary arithmetic and data representation methods.

#### 1.3 NUMBER SYSTEM

Number system is a fundamental concept used in micro computer system. They are of different types and can be represented by digit symbols. The knowledge of binary, octal and hexadecimal number system is essential to understand the operation of a computer. This unit deals with all these number systems. In this unit we will discuss about all the representation of number system and their conversion from one number system to another number system.

We are familier with the decimal number system which is used in our day-to-day work. Ten digits are used in decimal number system. To represent these decimal digits, ten separate symbols 0, 1, 2, 3, 4, 5, 6, 7, 8 and 9 are used. But a digital computer stores, understands and manipulates information composed of only zeros and ones. So, each decimal digits, letters, symbols etc. written by the programmer (an user) are converted to binary codes in the form of 0's and 1's within the computer. The number system is divided into different categories according to the base (or radix) of the system as binary, octal and hexadecimal. If a number system of base r is a system, then the system have r distinct symbols for r digits. The knowledge of the number system is essential to understand the operation of a computer.

#### 1.3.1 Decimal Number System

Decimal number system have ten digits represented by 0, 1, 2, 3, 4, 5, 6, 7, 8 and 9. So, the base or radix of such a system is 10.

In this system, the successive position to the left of the decimal point represent units, tens, hundreds, thousands etc. For example, if we consider a decimal number 1257, then the digit representations are :

| 1         | 2        | 5        | 7        |

|-----------|----------|----------|----------|

| Ļ         | ↓        | ↓        | Ļ        |

| thousands | hundreds | tens     | units    |

| positions | position | position | position |

The weight of each digit of a number depends on its relative position

within the number.

**Example 1.1** : Find the weight of each digit in 6472.

The weight of each digit of the decimal no. 6472

$6472 = 6000 + 400 + 70 + 2 = 6 \times 10^3 + 4 \times 10^2 + 7 \times 10^1 + 2 \times 10^0$

The weight of digits from right hand side are :

Weight of 1st digit =  $2 \times 10^{\circ}$

Weight of 2nd digit =  $7 \times 10^{1}$

Weight of 3rd digit =  $4 \times 10^2$

Weight of 4th digit =  $6 \times 10^3$

The above expressions can be written in general forms as the weight of  $n^{th}$  digit of the number from the right hand side :

$= n^{th} digit \times 10^{n-1}$

= n<sup>th</sup> digit × (base)<sup>n-1</sup>

The number system in which the weight of each digit depends on its relative position within the number is called positional number system. The above form of general expression is true only for positional number system.

#### 1.3.2 Binary Number System

Only two digits 0 and 1 are used to represent the binary number system. So the base or radix is two (2). The digits 0 and 1 are called bits (Binary Digits). In this number system the value of the digit will be two times greater than its predecessor. Thus, the value of the places are :

$\leftarrow 32 \leftarrow 16 \leftarrow 8 \leftarrow 4 \leftarrow 2 \leftarrow 1$

The weight of each binary bit depends on its relative position within the number. It is explained by the following example--

Decimal Number System uses 10 digits from 0 to 9.

**Example 1.2**: Find the weight of binary number 10110.

The weight of bits of the binary number 10110 is :

$= 1 \times 2^{4} + 0 \times 2^{3} + 1 \times 2^{2} + 1 \times 2^{1} + 0 \times 2^{0}$

= 16 + 0 + 4 + 2 + 0 = 22 (decimal number)

The weight of each bit of a binary no. depends on its relative

pointer within the no. and explained from right hand side as :

Weight of 1st bit = 1st bit X 2<sup>o</sup>

Weight of 2nd bit = 2nd bit  $X 2^{1}$

.....

.....

and so on.

The weight of the n<sup>th</sup> bit of the number from right hand side

$= n^{th} bit \times 2^{n-1}$

= n<sup>th</sup> bit x (Base)<sup>n-1</sup>

It is seen that this rule for a binary number is same as that for a decimal number system. The above rule holds good for any other positioned number system. The weight of a digit in any positioned number system depends on its relative positon within the number and the base of the number system.

Table 1.1 shows the binary equivalent numbers for decimal digits.

| Decimal Number | Equivalent Binary Number |

|----------------|--------------------------|

| 0              | 0                        |

| 1              | 1                        |

| 2              | 10                       |

| 3              | 11                       |

| 4              | 100                      |

| 5              | 101                      |

| 6              | 110                      |

| 7              | 111                      |

| 8              | 1000                     |

| 9              | 1001                     |

Table 1.1 : Binary equivalent of decimal numbers

A Binary Number

System uses only digit 0 and 1

**Binary Fractions :** A binary fractions can be represented by a series of 1s and 0s to the right of a binary point. The weight of digit positions to the right of the binary point are given by  $2^{-1}$ ,  $2^{-2}$ ,  $2^{-3}$  and so on.

**Example 1.3 :** Show the representation of binary fraction 0.1101.

Solution : The binary representation of 0.1101 is :

$0.1101 = 1 \times 2^{-1} + 1 \times 2^{-2} + 0 \times 2^{-3} + 1 \times 2^{-4}$ = 1 \times 0.5 + 1 \times 0.25 + 0 \times 0.125 + 1 \times 0.0625 = 0.8125 So, (0.1101)<sub>2</sub> = (0.8125)<sub>10</sub>

#### 1.3.3 Octal Number System

A commonly used positional number system is the Octal Number System. This system has eight (8) digit representation as 0,1,2,3,4,5,6 and 7. The base or radix of this system is 8. The values increase from left to right as 1,8,64,512,4096 etc. The decimal value 8 is represented in octal as 10,9 as 11,10 as 12 and so on. As  $8=2^3$ , an octal number is represented by a group of three binary bits. For example, 3 is represented as 011, 4 as 100 etc.

| Decimal Number | Octal Number | Binary Coded Octal No. |

|----------------|--------------|------------------------|

| 0              | 0            | 000                    |

| 1              | 1            | 001                    |

|                |              |                        |

|                |              |                        |

| 7              | 7            | 111                    |

| 8              | 10           | 100 000                |

| 15             | 17           | 001 111                |

Table 1.2 The octal number and their binary representations.

#### 1.3.4 Hexadecimal Number System

The hexadecimal number system is now extensively used in computer industry. Its base (or radix) is 16, and the digits are 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F. The hexadecimal numbers are used to represent binary numbers incase of conversion and compactness.

Octal Number System uses 8 digits from 0 to 7.

As  $16 = 2^4$ , hexadecimal number is represented by a group of four binary bits. For example, 5 is represented by 0101. Table 1.3 shows the binary equivalent of a decimal number and its hexadecimal representation.

| Decimal No. | Hexadecimal No. | Binary coded Hex. No |

|-------------|-----------------|----------------------|

| 0           | 0               | 0000                 |

| 1           | 1               | 0001                 |

| 2           | 2               | 0010                 |

| 3           | 3               | 0011                 |

| 4           | 4               | 0100                 |

| 5           | 5               | 0101                 |

| 6           | 6               | 0110                 |

| 7           | 7               | 0111                 |

| 8           | 8               | 1000                 |

| 9           | 9               | 1001                 |

| 10          | А               | 1010                 |

| 11          | В               | 1011                 |

| 12          | С               | 1100                 |

| 13          | D               | 1101                 |

| 14          | E               | 1110                 |

| 15          | F               | 1111                 |

Table 1.3 : Hexadecimal number and their Binary representation

#### 1.4 NUMBER SYSTEM CONVERSION

As the computer uses different number systems, there is a process of converting generally used decimal number systems to other number systems and vice-versa.

#### 1.4.1 Binary to Decimal Conversion

To convert a binary number to its decimal equivalent we use the following expression. The weight of the n<sup>th</sup> bit of the number from right hand side can be represented as-

Unit 1

$= n^{th} bit \times 2^{n-1}$

First we mark the bit position and then we give the weight of each bit of the number depending on its position. The sum of the weight of all bits gives us the equivalent number.

**Example 1.4 :** Convert binary (100101)<sub>2</sub> to its decimal equivalent.

Solution:

$$(100101)_2$$

= 1 × 2<sup>5</sup> + 0 × 2<sup>4</sup> + 0 × 2<sup>3</sup> + 1 × 2<sup>2</sup> + 0 × 2<sup>1</sup> + 1 × 2<sup>0</sup>

= 32 + 0 + 0 + 4 + 0 + 1

= 37

So,  $(100101)_2$  =  $(37)_{10}$

Mixed number contain both integer and fractional parts and can convert to its decimal equivalent is as follows :

**Example 1.5 :** Convert (11011.101)<sub>2</sub> to its equivalent decimal number.

Solutaion :

$$(11011.101)_{2} = (1 \times 2^{4} + 1 \times 2^{3} + 0 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0}) + (1 \times 2^{-1} + 0 \times 2^{-2} + 1 \times 2^{-3}) = (16 + 8 + 0 + 1) + (0.5 + 0 + 0.125) = 27.625$$

So,  $(11011.101)_{2} = (27.625)_{10}$

#### 1.4.2 Decimal to Binary Conversion

There are different methods used to convert decimal number to binary numbers. The most common method is to repeatedly divide the decimal number by 2, then the remainder 0's and 1's obtained after division, is read in reverse order to obtain the binary equivalent of the decimal number. **Example 1.6 :** Convert (75)<sub>10</sub> to its binary equivalent.

| Solution | 2   <u>75</u>                  |                   | Rem | nainder       |

|----------|--------------------------------|-------------------|-----|---------------|

|          | 2   <u>37</u>                  | LSB               | 1   |               |

|          | 2 <u> 18</u>                   |                   | 1 ấ | i             |

|          | 2   <u>9</u>                   |                   | 0   | Read in       |

|          | 2   <u>4</u>                   |                   | 1   | reverse order |

|          | 2   <u>2</u>                   |                   | 0   |               |

|          | 2   <u>1</u>                   | MSB               | 0   |               |

|          | 0                              |                   | 1   |               |

|          | So, (75) <sub>10</sub> = (1001 | 011) <sub>2</sub> | I   |               |

**Example 1.7 :** Convert decimal fraction  $(25.625)_{10}$  to its equivalent binary number.

| Solution : 2 25         | Rem          | ainder | MSB | 0.625      |   |

|-------------------------|--------------|--------|-----|------------|---|

|                         | 2 <u> 12</u> | 1      | ę   | <u>× 2</u> |   |

|                         | 2 <u> 6</u>  | 0      |     | 1.250      |   |

|                         | 2   <u>3</u> | 0      |     | <u>× 2</u> |   |

|                         | 2   <u>1</u> | 1      |     | 0.500      | â |

|                         | 0            | 1      |     | <u>× 2</u> |   |

| $(25)_{10} = (11001)_2$ |              |        |     | 1.000      |   |

$(0.625)_{10} = (0.101)_2$ So,  $(25.625)_{10} = (11001.101)_2$

#### 1.4.3 Octal to Decimal Conversion

The method of converting octal numbers to decimal numbers is simple. The decimal equivalent of an octal number is the sum of the numbers multiplied by their corresponding weights.

Example 1.8: Find decimal equivalent of octal number (153)<sub>8</sub>

**Solution :**  $1 \times 8^2 + 5 \times 8^1 + 3 \times 8^0 = 64 + 40 + 3 = 107$

So,  $(153)_8 = (107)_{10}$

The fractional part can be converted by multiplying it by the negative powers of 8 as shown in the following example.

Example 1.9: Find decimal equivalent of octal number (123.21)<sub>8</sub>

**Solution :**  $(1X8^2 + 2X8^1 + 3X8^0) + (2 \times 8^{-1} + 1 \times 8^{-2})$

= (64 + 16 + 3) + (0.25 + 0.0156) = 83.2656

#### 1.4.4 Decimal to Octal Conversion

The procedure for conversion of decimal numbers to octal numbers is exactly similar to the conversion of decimal number to binary numbers except replacing 2 by 8.

Example 1.10 : Find the octal equivalent of decimal (4121)<sub>10</sub>

14

#### Solution :

| 8 <u> 4121</u> |                |               |

|----------------|----------------|---------------|

| 8 <u> 515</u>  | <sup>1</sup> á | read from MSB |

| 8 <u> 64</u>   | 3              | to LSB        |

| 8 <u> 8</u>    | 0              |               |

| 8   <u>1</u>   | 0              |               |

| 0              | 1              |               |

|                |                |               |

So, (4121)<sub>10</sub>=(10031)<sub>8</sub>

The fractional part is multiplied by 8 to get a carry and a fraction as

shown in the following example.

Example 1.11 : Find the octal equivalent of (.123)<sub>10</sub>

Solution : Octal equivalent of fractional part of the decimal number is :

$$8 \times 0.123 = 0.984$$

0

$8 \times 0.984 = 7.872$  7

$8 \times 0.872 = 6.976$  6

$8 \times 0.976 = 7.808$  7

to MSB

Read the integer to the left of the decimal point.

The calculation can be terminated after a few steps if the fractional part does not become zero.

The octal equivalent of  $(0.123)_{10} = (0.0767)_8$

**NOTE :** The octal to binary and binary to octal conversion is very easy. Since, 8 is the third power of 2, we can convert each octal digit into its threebit binary form and vice versa.

**Example 1.12** : Convert  $(567)_8$  to its binary form.

Solution: 5 6 7

$$\downarrow$$

$\downarrow$   $\downarrow$   $\downarrow$

101 110 111

So, (567)<sub>8</sub> = (101 110 111)<sub>2</sub>

Conversion from binary to octal is just opposite of the above

example.

#### 1.4.5 Hexadecimal to Decimal Conversion

The method of converting hexadecimal numbers to decimal numbers

is simple. The decimal equivalent of an hexadecimal number is the sum of

the numbers multiplied by their corresponding weights.

**Example 1.13**: Find the decimal equivalent of (4A8C)<sub>16</sub> **Solution**:

$(4A8C)_{16} = (4 \times 16^{3}) + (10 \times 16^{2}) + (8 \times 19^{1}) + (12 \times 16^{0})$ = 16384 + 2560 + 128 + 12 $= (19084)_{10}$  $(4A83)_{16} = (19084)_{10}$ **Example 1.14**: Find the decimal equivalent of (53A.0B4)\_{16}

Solution :

$(53A.0B4)16 = (5 \times 16^{2}) + (3 \times 16^{1}) + (10 \times 16^{0}) + (0 \times 16^{-1})$  $+ (11 \times 16^{-2}) + (4 \times 16^{-3})$ = 1280 + 48 + 10 + 0 + 0.04927 + 0.0009765 $= (1338.0439)_{10}$  $(53A.0B4)_{16} = (1338.0439)_{10}$

#### 1.4.6 Decimal to Hexadecimal Conversion

The procedure for conversion from decimal no. and its fraction part to hexadecimal equivalent is exactly similar to the conversion of decimal to binary number except replacing 2 by 16.

**Example 1.15 :** Convert decimal (1234.675)<sub>10</sub> to hexadecimal.

**Solution :** First, we consider  $(1234)_{10}$ :

|                              | Rem                     | ainde                       | r                |             |

|------------------------------|-------------------------|-----------------------------|------------------|-------------|

|                              | Decimal                 | Hex                         | ade              | cimal       |

| 16 <u> 1234</u>              | 2                       | á                           | 2                |             |

| 16 <u> 77</u>                | 13                      |                             | D                |             |

| 16 <u> 4</u>                 | 4                       |                             | 4                |             |

| $(1234)_{10} = (4D2)_{10}$   | 2) <sub>16</sub>        |                             |                  |             |

| Then, conversion             | on of (0.67             | ′ <b>5)</b> <sub>10</sub> : |                  |             |

|                              | D                       | ecima                       | al I             | Hexadecimal |

| 0.675 × 16 =                 | = 10.8                  | 10                          |                  | А           |

| 0.800 × 16 =                 | = 12.8                  | 12                          |                  | С           |

| 0.800 × 16 =                 | = 12.8                  | 12                          |                  | С           |

| 0.800 × 16 =                 | = 12.8                  | 12                          | 4                | С           |

| $(0.675)_{10} = (0.A0)_{10}$ | CC) <sub>16</sub>       |                             | č                | 3           |

| Hence (1234.67               | 75) <sub>10</sub> = (4D | 2.AC                        | C) <sub>16</sub> |             |

If the decimal number is very large, it is tedious to convert the number to binary directly. So it is always advisable to convert the number into hexadecimal first, and then convert the hexadecimal to binary.

## 1.5 LET US SUM UP

- We have learnt four different number systems used in digital systems in this unit.

- Conversion of one number system to another number system can be done.

- I In our day-to-day life, we use the decimal number system. In this system, base is 10 and we use 10 digits from 0 to 9.

- I The binary number system has two digits and so its base is 2.

- I The octal number system has 8 digits from 0 to 7 and the base of the system is 8.

- I The hexadecinal number system has 16 digits from 0 to 9 and A to F and the base of the system is 16.

# R

# **1.6 FURTHER READING**

- Ram, B. (2000), Computer Fundamentals Architecture and Organization, New Age International

- I Mano, M.M. (2017), Digital Logic and Computer Design, Pearson Education India

- I Sinha, P. K. and Sinha P. (2010), Computer Fundamentals, BPB Publication.

- I Talukdar, P. (2010), Digital Techniques, N.L. Publications.

# ANSWERS TO CHECK YOUR PROGRESS

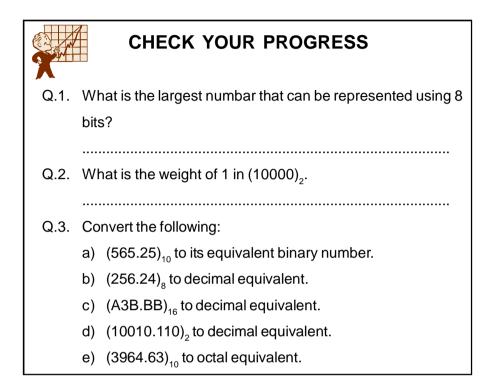

**Ans. to Q. No. 1**: (1111 1111)<sub>2</sub>

**Ans. to Q. No. 2**: Weight is 2<sup>4</sup> = 16

Ans. to Q. No. 3: a)  $(1000110101.01)_2$  b)  $(174.44)_{10}$  c)  $(2620.8)_{10}$ d)  $(18.75)_{10}$  e)  $(7574.50)_8$

#### 1.8 MODEL QUESTIONS

- Q.1.What is binary number system?

- Q.2.What is meant by 'base' or 'radix' of a number system?

- Q.3.Convert the following to its binary equivalent:

- (i) (67)<sub>8</sub> (ii) (A8D)<sub>16</sub> (iii) (81B6.F)<sub>16</sub>

- (iv)  $(64.3)_{10}$  (v)  $(765.45)_8$  (vi)  $(1725.23)_8$

- Q.4. Convert the following to its decimal equivalent:

- (i)  $(11011)_2$  (ii)  $(1111.11)_2$  (iii)  $(45)_8$

- (iv)  $(671.23)_8$  (v)  $(ABCD)_{16}$  (vi)  $(12AF.E4)_{16}$

- Q.5.Explain the process of converting a decimal number to binary.

- Q.6.How can a binary number be converted into octal and hexadecimal numbers?

\*\*\*\*\*\*

## **UNIT 2 : BINARY ARITHMETIC**

## UNIT STRUCTURE

- 2.1 Learning Objectives

- 2.2 Introduction

- 2.3 Complement of Numbers

- 2.3.1 (r-1)'s Complement

- 2.3.2 r's Complement

- 2.4 Binary Arithmetic

- 2.4.1 Addition

- 2.4.2 Subtraction

- 2.4.3 Multiplication

- 2.4.4 Division

- 2.5 Let Us Sum Up

- 2.6 Further Reading

- 2.7 Answers to Check Your Progress

- 2.8 Model Questions

## 2.1 LEARNING OBJECTIVES

After going through this unit you will be able to:

- I describe r's and (r-1)'s complement

- I describe binary addition and subtraction

- I describe binary multiplication and division.

## 2.2 INTRODUCTION

In the previous unit, we have been introduced to the different number systems Decimal, Octal, Binary and Hexadecimal. We have also learnt how to convert from one number system to another number system in the previous unit. In this unit, we will learn about the complement systems. We will learn about R and (R-1)'s complement systems. We will also learn to perform binary arithmetic functions like addition, subtraction, multiplication and division in this unit. In the next few units are will learn more about data representation and code conversion methods.

## 2.3 COMPLEMENT OF NUMBERS

The 7's and 15's complement of a number is found by subtracting each digit of the number from 7 and 15 respectively. Complements are used in digital computers for simplifying the substraction operation and for logical manipulation. The complement of a binary number is obtained by inverting all of the bits.

For example, the complement of 10011 is 01100 and 00101 is 11010 etc. The complement again depends on the base of the number.

There are two types of complements for a number of base r. These are :

- r's complement and

- I (r-1)'s complement,

For example, for decimal numbers the base is 10. Therefore, complements will be 10's complement and (10-1)=9's complement. For binary numbers, the complement are 2's complement and 1's complement since base is 2.

## 2.3.1 (r-1)'s Complement

Given a number N in base r having n digits, the (r-1)'s complement of N is defined as  $(r^n-1) - N$ .

**9's Complement :** For decimal numbers, r=10 and r-1=9, so the 9's complement of N is  $(10^{n}-1) - N$ .

For example, with n = 4 we have  $10^4 = 10000$  and  $10^4 - 1 = 9999$ . It follows the rule that the 9's complement of a decimal number is obtained by subtracting each digit from 9.

For example, 9's complement of 49 is (99–49) = 50

9's complement of 127 is (999–127) = 872

**1's Complement :** For binary numbers, r = 2 and (r-1) = 1, so the 1's complement of N is  $(2^n-1) - N$ . Again,  $2^n$  is represented by a binary number that consists of a 1 followed by n 0's.  $2^n-1$  is a binary number represented by n 1's. For example, with n = 4, we have  $2^4 = (10000)_2$  and  $2^4-1 = (1111)_2$ . Thus the 1's complement of a binary number is obtained by subtracting each digit from 1.

However, the subtraction of a binary digit from 1 causes the bit to change from 0 to 1 or from 1 to 0. Therefore, the 1's complement of a binary number is formed by changing 1's into 0 and 0's into 1's. For example, 1's complement of 1010111 is 0101000.

Like 8's complement and 16's complement of a number is found by adding 1 to the LSB of the 7's and 15's complement of an octal and hexadecimal number respectively.

#### 2.3.2 R's Complement

The r's complement of a n-digit number N in base r is defined as  $r^n - N$  for N =0 and 0 for N = 0. Comparing with the (r–1)'s complement, we note that the r's complement is obtained by adding 1 to the (r–1)'s complement.

**10's Complement :** The 10's complement of a decimal number is equal to the 9's complement of the number plus 1

i.e. 10's complement of decimal number = Its 9's complement +1

So, 10's complement of 49 is (99-49) + 1 = 50 + 1 = 51

10's complement of 127 is (999–127) + 1 = 872 + 1 = 873

2's Complement : It is obtained by adding 1 in the 1's complement form of the binary numbers.

i.e. 2's complement of binary number = 1's complement of that number + 1

For example, 2's complement of 1010111 is 0101000 + 1 = 0101001

#### 2.4 BINARY ARITHMETIC

Like decimal arithmetic operations such as addition, subtraction we

can perform arithmetic operation in binary number system too.

#### 2.4.1 Addition

Binary addition is performed in the same manner as decimal addition. Since,

in binary system only two digit 0 and 1 are used, the addition follows the following rules.

0 + 0 = 0 0 + 1 = 1 = 1 + 0 1 + 1 = 0, Carry 1 to the next left column 1 + 1 + 1 = 1, Carry 1 to the next column.

Carry overs are performed in the same manner as in decimal arithmetic.

Example 2.1 : Add the binary numbers

| (i) 1011 | and 1001 |

|----------|----------|

|----------|----------|

(ii) 10.011 and 1.001

Solution :

| (i) | Binary no.   | Equivalent decimal no. |

|-----|--------------|------------------------|

|     | 11 Carry     |                        |

|     | 1011         | 11                     |

|     | <u>+1001</u> | _9                     |

|     | 10100        | 20                     |

|     |              |                        |

|      | 1 Carry      |              |

|------|--------------|--------------|

| (ii) | 10.011       | 2.375        |

|      | <u>1.001</u> | <u>1.125</u> |

|      | 11.100       | 3.500        |

Since the circuit in all digital systems actually can handle two numbers to performs addition, it is not necessary to consider the addition of more than two binary numbers. When more than two numbers are to be added, the first two are added first and then their sum is added to the third and so on.

The complexity may rise when we add combination of positive and negative binary numbers. In this case, the arithmatic addition is dependent on the representation of

a) Signed magnitude

- b) Signed 1's complement

- c) Signed 2's complement

This will be more clear if we discuss using the following example:

**Example 2.2**: Add 25 and -30 in binary using 7 bit register in signed magnitude representation

- a) Signed 1's complement representaion

- b) Signed 2's complement representaion

**Solution :** Here, 25 is + 25

+ 25 = 0011001 in binary system

-30 = 1011110 in binary system

To do arithmatic addition with one negative number, we have to check the magnitude of the numbers. The number having smaller magnitude is subtracted from the bigger number and the sign of bigger number is selected. To implement such a scheme in digits, hardware will require a long sequence of control decisions as well as circuits that will add, compare and subtract numbers. The better alternative of arithmatic addition with one negative number is signed 2's complement.

#### In signed 2's complement representation :

| We get that                                              | +30 is   | 0          | 011110           |      |         |  |

|----------------------------------------------------------|----------|------------|------------------|------|---------|--|

|                                                          | –30 is   | 1          | 011110           |      |         |  |

| Now, 2's complement of -30 (including sign bit) 1 100010 |          |            |                  |      |         |  |

|                                                          |          | -          | ⊦25 is           | 0    | 011001  |  |

| Addition                                                 |          |            |                  |      |         |  |

| +25                                                      | 0        | 011        | 001              |      |         |  |

| <u>30</u>                                                | <u>1</u> | <u>100</u> | <u>010</u>       |      |         |  |

| -05                                                      | 1        | 111        | 011 (Just add th | ie n | umbers) |  |

The result for negative number will store in signed 2's complement form. So the above result in signed 2's complement form including sign bit is:

1 000 100 +1 = 1 000 101 Which is -05 in decimal system.

From the above example, it can be noticed that, signed 2's complement representation is simpler than signed magnitude representation. This procedure requires only one central decision and only one circuit for adding the two numbers. But it puts additional condition that the negative numbers should be stored in signed 2's complement form in the register. This can be achieved by complementing the positive number bit by bit then incrementing the resultant by 1 to get signed 2's complement.

Digital Techniques

**In signed 1's complement representation :** This method is also simple. Here, we add the two numbers including the sign bit. If carry of the most significant bit or sign bit is one, then we increment the result by 1 and discard the carry over.

Addition :

| +25        | = | 0        | 011 001                         |

|------------|---|----------|---------------------------------|

| <u>–30</u> | = | <u>1</u> | 100 001 (1's complement of -30) |

| -5         | = | 1        | 111 010                         |

The result will store in 1's complement format. So, 1111 010 in 1's complement format including the sign bit is 1 000 101 which is the required result.

Example 2.3 : Add -25 and +30 using 7-bit register.

Solution :

| -25        | 1        | 100        | 110        | (1's complement of 25) |

|------------|----------|------------|------------|------------------------|

| <u>+30</u> | <u>0</u> | <u>011</u> | <u>110</u> |                        |

| +5         | 10       | 000        | 100        |                        |

|            | 1        |            |            |                        |

Carry bit, so add 1 to the sum and discard the carry.

This sum is now = 0 000 101 which is +5

Example 2.4 : Add –25 and –30 using 7-bit register.

| Solution : | -25        | 1        | 100        | 110 (1's complement of 25) |

|------------|------------|----------|------------|----------------------------|

|            | <u>–30</u> | <u>1</u> | <u>100</u> | 001 (1's complement of 30) |

|            | -55        | 11       | 000        | 111                        |

|            |            | ↑        |            |                            |

Carry bit, so add 1 to sum and discard the carry.

Now the sum is = 1 001 000, which is -55

Since, +55 is 0 110 111

So, -55 is in 1's complement 1 001 000

The interesting feature about these representation is the representation of 0 in signed magnitude and 1's complement. There are two representations for zero :

Signed magnitude +0 –0

|            |         |                      | 0     | 0000  | 00     | 1     | 000000         |

|------------|---------|----------------------|-------|-------|--------|-------|----------------|

|            | Sign    | ed 1's complement    | 0     | 0000  | 00     | 1     | 111111         |

|            | But i   | n signed 2's compler | nent, | there | is jus | t one | zero and there |

| are no pos | itive o | or negative zero.    |       |       |        |       |                |

|            | +0      | 000000               |       |       |        |       |                |

|            | -0      | in 2's complement is | s +0  | =     | 1 1    | 11111 | 1              |

|            |         |                      |       |       |        |       | 1              |

|            |         |                      | 1     |       | 0 0    | 0000  | 0              |

|            |         |                      | ↑     |       |        |       |                |

|            |         |                      | al:a  |       | h:     |       |                |

discard this carry

Thus, both +0 and -0 are same in 2's complement notation. This is an *added advantage* in favour of 2's complement notation. The maximum number which can be accomodated in registers also depends on the type of representation. In general, in a 8 bit register, 1 bit is used as sign. Therefore, the rest of 7 bits are used for representing the value. The value of maximum and minumum number which can be represented are :

For signed magnitude representation  $2^7 - 1$  to  $-(2^7 - 1)$

= 128 -1 to - (128-1) = 127 to - 127,

which is for signed 1's complement representation.

For signed 2's complement representation is from + 127 to -128. The -128 is represented in signed 2's complement notation as 10000000.

#### 2.4.2 Subtraction

Though there are many other methods for performing subtraction, we will consider the method of subtraction known as complementary subtraction. This is a more efficient method of subtraction while using electronic circuits. We have to follow the following three steps to subtract binary numbers.

#### In 1's complement method :

- 1. Find the 1's complement of the number which is subtracting.

- Add the number which is subtracting from with the complement value obtained from step 1.

3. If there is a carry of 1, add the carry with the result of addition. Else, take complement of the result again and attach a negative sign with the result.

**Example 2.5**: Subtract 5 – 6 by 1's complement method.

| Solution : | Binary equivalent of 5 is | 101 |

|------------|---------------------------|-----|

|            |                           |     |

| Binary equivalent of 6 is | 110 |

|---------------------------|-----|

|---------------------------|-----|

Step 1 : 1's complement of 6 is 001

Step 2 : Adding 001 with 101 gives the result :

001 <u>+ 101</u> 110

Step 3 : Since there is no carry in step 2, we take the complement again which will be 001 and after attaching negative sign, the required result will be –001 which is -1.

**In 2's complement method :** It is same as 1's complement method except step 3. The steps are :

Step 1 : Find the 2's complement of the number which is subtracting.

Step 2 : Add the number which is subtracting from, with the complement value obtained from step 1.

Step 3 : If there is a carry of 1, ignore it. Else, take 2's complement of the result again and attach a negative sign with the result.

**Example 2.6 :** Subtract 5 – 7 by 2's complement method.

| Solution : | Binary equivalent of 5 is | 101 |

|------------|---------------------------|-----|

|            |                           |     |

Binary equivalent of 7 is 111

Step 1 : The 2's complement of 7 is 000 + 1 = 001

Step 2 : Adding 001 with 101 will give result as :

001

#### <u>101</u>

110 (No carry)

Step 3 : Since there is no carry, the 2's complement of 110 is 001 + 1 = 010and attaching a negative sign the required result is -10 i.e., -2. **Overflow :** An overflow is said to have occured when the sum of two n digit

number occupies (n+1) digits. This definition is valid for both binary as well

#### **Binary Arithmetic**

as decimal digits. But what is the significance of overflow for binary numbers? Well, the answer lies in the representation of numbers. Every computer employs a limit for representation of numbers eg. in our examples we are using 8 bit registers of calculating the sum. But what will happen if the sum of the two numbers can be accommodated only in 9 bits? Where are we going to store the 9th bit? The problem will be more clear by the following example. In case of a +ve no. added to a –ve no., the sum of result will always be smaller than the two numbers. An overflow always occurs when the added numbers are both +ve or both -ve.

**Example 2.7 :** Add the numbers 65 and 75 in 8 bit register in signed 2's complement notation.

| Solution : | 65        | 0        | 1000001        |

|------------|-----------|----------|----------------|

|            | <u>75</u> | <u>0</u> | <u>1001011</u> |

|            | 140       | 1        | 0001100        |

This is a -ve number and the 2's complement of the result is equal to -115 which is obviously a wrong result. This has occured because of overflow.

Detection of Overflow : Overflow can be detected as :

If the carry out of the MSBs of number (or, carry into the sign bit) is equal to the carry out of the sign bit, then overflow must have occured. For example

|     | -65        | 1        | 0111111        | -65      | 1        | 0111        | 111        |

|-----|------------|----------|----------------|----------|----------|-------------|------------|

|     | <u>–15</u> | <u>1</u> | <u>1110001</u> | <u> </u> | <u>1</u> | <u>0110</u> | <u>101</u> |

|     | -80        | 11       | 0110000        | -140     | 10       | 1110        | 100        |

| Са  | rry        |          | = 1            | Carry    |          |             | = 10       |

| Са  | rry fro    | m MSE    | 3 = 1          | Carry f  | from M   | ISB         | = 0        |

| Са  | rry fro    | m sign   | bit = 1        | Carry f  | rom si   | gn bit      | = 1        |

| Sig | n bit i    | S        | = 1            | Sign b   | it is    |             | = 0        |

| No  | overfl     | ow       |                | Overflo  | w        |             |            |

Thus, overflow has occured, i.e. the arithmatic results so calculated have exceeded the capacity of the representation. This overflow also implies that the calculated results might be errorneous.

#### 2.4.3 Multiplication

Multiplication in binary follows the same rules that are followed in the decimal system. The rules to be remembered are:

$$0 \times 0 = 0 \qquad 1 \times 0 = 0$$

$$0 \times 1 = 0 \qquad 1 \times 1 = 1$$

For example, multiplying 10101 × 11001

10101

10101

10101

1000001101

#### 2.4.4 Division

The process of binary division is same as the decimal division. In binary division we have two rules:

$$0/1 = 0$$

$1/1 = 1$

The steps for binary division are :

- 1. Start from the left of the divided.

- 2. Perform subtraction in which the divisor is subtracted from the divedend.

- a) If subtraction is possible put a 1 in the quotient and subtract the divisor from the corresponding digits of the dividend. Else put a 0 in the quotient

- b) Bring down the next digit to the right of the remainder.

- 3. Execute step 2 till there are no more digits left to bring down from the dividend.

Example 2.8 : Divide 1011001 by 110

Solution :

<u>0111</u> (Quotient) (Divisor) 110 |1011001 (Dividend) <u>110</u> 1010 <u>110</u> 1000 <u>110</u> 0101

Here 111 is the quotient and 101 is the remainder.

| CHECK YOUR PROGRESS                                                  |

|----------------------------------------------------------------------|

| Q.3.Add 35 and -40 in binary using 7 bit register in 2's complement  |

| representation.                                                      |

|                                                                      |

| Q.4.Add binary no. 110011.010 and 1000.10                            |

|                                                                      |

| Q.5.Subtract $(1010101)_2$ - $(1001001)_2$ by 2's complement method. |

|                                                                      |

| Q.6.Multiply $(11001)_2$ by $(101)_2$ .                              |

|                                                                      |

| Q.7.Divide $(101101.101)_2$ by $(110)_2$ .                           |

|                                                                      |

# 2.5 LET US SUM UP

- I The 1's complement of a binary number is formed by changing 1's into 0 and 0's into 1's.

- I The 2's complement of a binary number is obtained by adding 1 to the 1's complement of the binary number.

- I Binary addition is performed in the same manner as decimal addition.

- Complementary subtraction method is considerd for binary subtraction.

- An overflow is said to have occured when the sum of two n digits number occupies (n+1) digits.

# **2.6 FURTHER READING**

- Ram, B. (2000), Computer Fundamentals Architecture and Organization, New Age International

- I *Mano, M.M. (2017), Digital Logic and Computer Design*, Pearson Education India

- I Sinha, P. K. and Sinha P. (2010), Computer Fundamentals, BPB Publication.

- I Talukdar, P. (2010), Digital Techniques, N.L. Publications.

# 2.7 ANSWERS TO CHECK YOUR PROGRESS

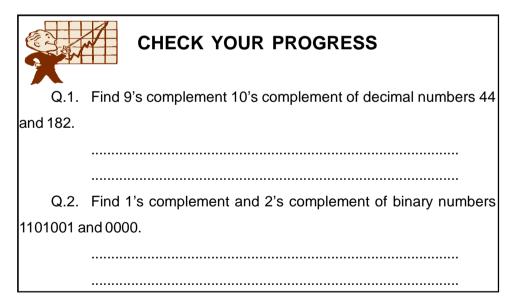

| Ans. to Q. No. 1 : | 9's complement of 44 is 55 and 182 is 817              |

|--------------------|--------------------------------------------------------|

|                    | 10's complement of 44 is 56 and 182 is 818             |

| Ans. to Q. No. 2 : | 1's complement of 1101001 is 0010110 and 0000 is       |

|                    | 1111                                                   |

|                    | 2's complement of 1101001 is 0010111 and 0000 is 10000 |

| Ans. to Q. No. 3 : | (000101) <sub>2</sub>                                  |

| Ans. to Q. No. 4 : | (111011.110) <sub>2</sub>                              |

| Ans. to Q. No. 5:  | (1100) <sub>2</sub>                                    |

| Ans. to Q. No. 6 : | (1111101) <sub>2</sub>                                 |

| Ans. to Q. No. 7 : | (111.10011) <sub>2</sub>                               |

# 2.8 MODEL QUESTIONS

- Q.1. Find 8's and 16's complement of the following: (i) 67 (ii) 5672

- Q.2. Find the 7's and 15's complement of the following: (i) 643 (ii) 15AB

- Q.3. Perform the following by 2's complement method: (i) 10101 – 11011 (ii) 100011 – 1111

- Q.4. Multiply 1101 to 11110.

- Q.5. Divide 110011 by 110.

\*\*\*\*\*\*

## **UNIT 3 : INTRODUCTION TO DATA REPRESENTATION**

## UNIT STRUCTURE

- 3.1 Learning Objectives

- 3.2 Introduction

- 3.3 Data Representation

- 3.4 Fixed Point Representation

- 3.5 Floating Point Representation

- 3.6 Let Us Sum Up

- 3.7 Further Reading

- 3.8 Answers to Check Your Progress

- 3.9 Model Questions

## 3.1 LEARNING OBJECTIVES

After going through this unit, you will be able to :

- I identify how data is represented in computers

- I describe fixed point representation

- I describe floating point representation

## 3.2 INTRODUCTION

In the previous units, we have learnt about different number systems like binary, octal, decimal and hexadecimal. We have also learnt how to do binary arithmetic operations like addition, subtraction, multiplication and division.

In this unit, we will discuss about the concept of data representation. Fixed and floating point representation are introduced in this unit. Floating point representation will be covered in detail in unit 7 later. In the next unit we will discuss about the different types of computer codes.

## 3.3 DATA REPRESENTATION

Data are usually represented by using the alphabets A to Z, numbers 0 to 9 and various other symbols. This form of representation is used to formulate problem and fed to the computer. The processed output is required

in the same form. This form of representation is called *external data representation*. However, the computer can understand data only in the form of 0's and 1's. The method of data representation in a form suitable for storing in the memory and for processing by the CPU is called the internal data representation on digital computer.

Data, in general, are of two types : Numeric and non-numeric (Character data). The numeric data deals only with numbers and arithmetic operations and non numeric data deals with characters, names, addresses etc. and non-arithmetic operations. Numeric data can be represented using fixed point or floating point representations. Let us look at these in detail.

#### 3.4 FIXED POINT REPRESENTATION

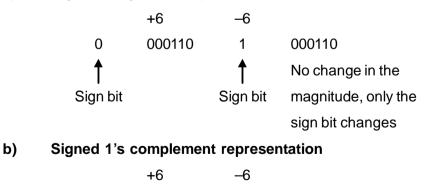

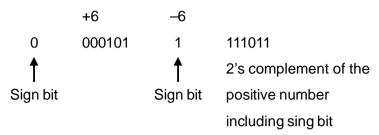

A fixed point number in binary system uses a sign bit. A positive number has a sign bit 0 while the negative number has a sign bit 1. A negative number can be represented in one of the following ways.

- Signed magnitude representaion

- Signed 1's complement representaion

- Signed 2's complement representation

Assume that the size of the register is 7 bit and the 8<sup>th</sup> position bit in used for error checking and correction or other purposes.

#### a) Signed magnitude representation

0

000110

Here 0 and 1 are sign bits. We get 1's complement for the –ve integer is by taking complement of all the bits of +ve no. including sign bit.

1

111001

#### c) Signed 2's complement representation

The signed magnitude system is easier to interpret but computer arithmetic with this system is not efficient. The circuits for handling numbers are simplified if 1's or 2's complement systems are used and as a result one of these two is almost always adopted.

**Note 1 :** In 1's and 2's complements, all positive integers are represented as sign magnitude system.

**Note 2**: When all the bits of the computer word are used to represent the number and no bit is used for signed representation, it is called unsigned representation of the number.

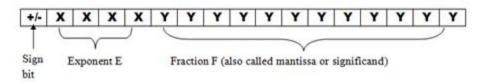

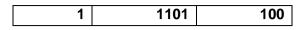

## 3.5 FLOATING POINT REPRESENTATION

A number which has both an integer part as well as a fractional part is called real number or floating point number. A floating point number is either positive or negative. Examples of real decimal numbers are 156.65, 0.893, -235.75, -0.253 etc. Examples of binary real numbers are 101.101, 0.11101, -1011.101, -0.1010 etc.

The first part of the number is a fixed point number which is called mantissa. It can be an integer or a fraction.

The second part specifies the decimal or binary point position and is termed exponent. It is not a physical point. Therefore, whenever we are representing a point it is termed as an exponent. It is only the assumed position. For example, for decimal 0. +15.37, the typical floating point notaion is :

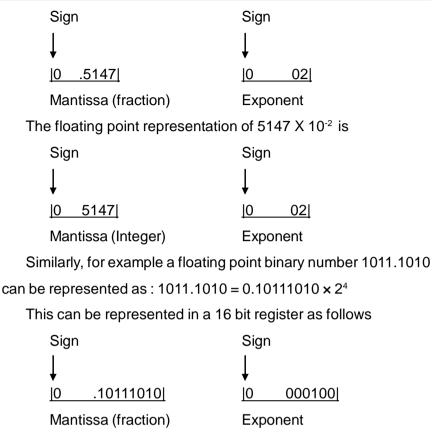

$51.47 = 0.5147 \times 10^2$  or  $5147 \times 10^{-2}$

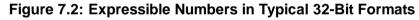

Now, the floating point representation of  $0.5147 \times 10^3$  is :

Unit 3

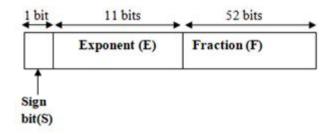

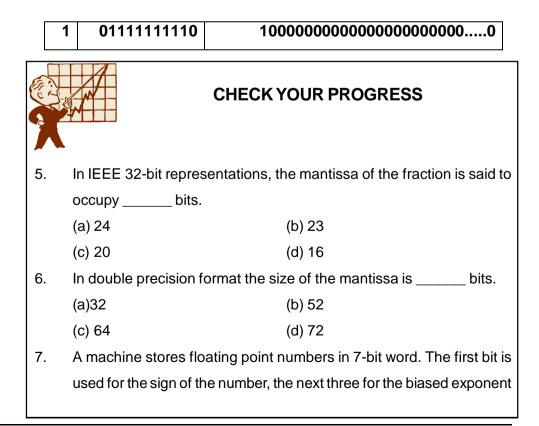

The mantissa occupies 9 bits (1 bit for sign and 8 bits for value) and the exponent 7 bits (1 bit for sign and 6 bits for value). The binary point (.) is not physically indicated in the register, but it is only assumed (position) to be there.

In general form, the floating point numbers is expressed as :

$N = M X R^{e}$

Where, M-Mantissa

R - Radix (or base)

e – Exponent

The mantissa M and exponent e are physically present in register. But the radix R and the point (decimal or binary point) are not indicated in the register. There are only assumed for computation and manipulation.

**Normalized Floating point Number :** Floating point numbers are often represented in normalized forms. A floating point number where mantissa does not contain zero as the most significant digit of the

number is considered to be in normaliged form. For example,  $0.00038695 \times 10^5$  and  $0.0589 \times 10^{-4}$  are not normaliged numbers. But  $0.38695 \times 10^2$  and  $0.589 \times 10^{-5}$  are normaliged numbers. Similarly, for binary number also,  $0.0011001 \times 2^8$  and  $0.0001011 \times 2^{-5}$ <sup>5</sup> are not non-normaliged binary numbers. But  $0.11001 \times 2^6$  and 0.1011 $\times 2^{-8}$  are normaliged binary numbers.

A zero cannot be normaliged as all the digits in the mantissa is zero.

Arithmetic operations involved with floating point numbers are more complex. It takes larger time for execution and requires complex hardware. But floating point representation is frequently used in scientific calculations.

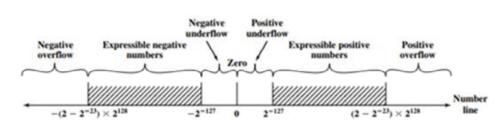

**Overflow and Underflow**: When the result is too small to be presented by the computer, an overflow or underflow condition exists. When two floating-point numbers of the same sign are added, a carry may be generated out of high-order bit position. This is known as mantissa overflow. In case of addition or subtraction floating point numbers are aligned. The mantissa is shifted right for the alignment of a floating point number. Sometimes, the low order bits are lost in the process of alignment. This is referred as mantissa underflow. To perform the multiplication of two floating point numbers, the exponents are added. In certain cases the sum of the exponents maybe too large and it may exceed the storing capacity of the exponent field. This is called exponent overflow. In case of division the exponent of the divisior is subtracted from the exponent of the division the result of subtraction may be too small to be represented. This is called exponent underflow.

Overflow or underflow resulting from a mantissa operation can be corrected by shifting the mantissa of the result and adjusting the exponent. But the exponent overflow or underflow can not be corrected and hence, an error indication has to be displayed on the computer screen.

#### 3.6 LET US SUM UP

- A fixed point numbers in binary system uses a sign bit. A positive number has a sign bit 0 while the negative number has a sign bit 1.

- I For fixed point we have discussed three different methods, they are:

- Ø Signed magnitude representation method

- Ø Signed 1's complement representation method

- Ø Signed 2's complement representation method

- I Signed magnitude representation: It uses one bit, usually the leftmost bit, to indicate the sign where '0' indicates the positive integer and the '1' indicates the negative integer. The rest of the bits are used as magnitude.

- I A number which has both an integer part and a fractional part is called real number or floating point number. A floating point number can be either positive or negative.

- The first part of the number is a fixed point number which is called

*Mantissa*. It can be an integer or a fraction.

- The second part specified the decimal or binary point position and is termed *exponent*.

- I A floating point number where mantissa does not contain zero as the most significant digit of the number is considered to be in normalized form.

- When two floating-point numbers of the same sign are added, a carry may be generated out of high-order bit position. This is known as mantissa overflow. In case of division the exponent of the divisor is subtracted from the exponent of the dividend. The result may be too small to be represented and is calaled exponent underflow.

## 3.7 FURTHER READING

- Morris, M.M. (1987). DIgital Logic and Computer Design.

- I Sinha, P.K., & Sinha, P. (2010). Computer Fundamentals (Vol. 4). BPB publications.

- Ram, B. (2000). Computer Fundamentals: Architecture and Organisation. New Age International.

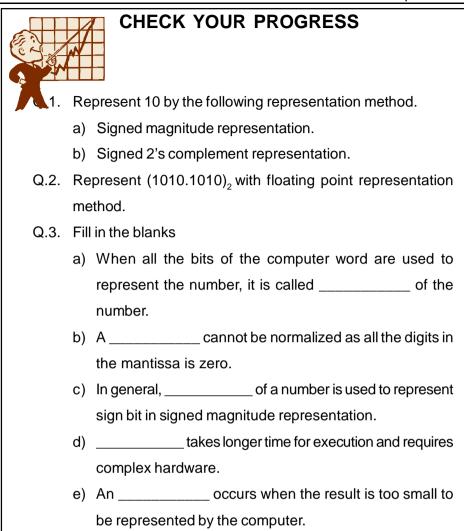

# 3.8 ANSWERS TO CHECK YOUR PROGRESS

- **Answer to Q1:** a) 001010

- b) 110110

- Answer to Q2: Mantissa is 10101010, fraction is 000100 (in 16 bit representation)

- Answer to Q3: a) unsigned representation

- b) zero

- c) leftmost bit

- d) Arithmetic operation

- e) overflow or underflow

#### **3.9 MODEL QUESTIONS**

- Q.1. Explain the fixed point representation method with example.

- Q.2. How can decimal number be represented?

- Q.3. What is mantissa and exponent of decimal representation?

- Q.4. How can a floating point number be normalized for computerized representation?

- Q.5. What is overflow and underflow?

- Q.6. What is data representation?

\*\*\*\*\*\*\*

## **UNIT 4 : CODE CONVERSION**

## UNIT STRUCTURE

- 4.1 Learning Objectives

- 4.2 Introduction

- 4.3 Computer Code

- 4.4 BCD number

- 4.5 ASCII Code

- 4.6 EBCDIC

- 4.7 Gray Code

- 4.8 Let Us Sum Up

- 4.9 Further Reading

- 4.10 Answers to Check Your Progress

- 4.11 Model Questions

## 4.1 LEARNING OBJECTIVES

After going through this unit, you will be able to :

- I describe different computer code systems

- I describe BCD and ASCII code

- I describe EBCDIC and Gray code

## 4.2 INTRODUCTION

In the previous units we have learned about different number systems like decimal, binary, octal and hexadecimal. We have also covered binary arithmetic operations like addition, subtraction multiplication and division. We have also discussed about the methods for representing data. Fixed point representation and floating point representation were also introduced in the previous unit.

In this unit, we will introduce the concept of computer code and code conversion. Different computer codes like BCD, ASCII, EBCDIC and gray codes are discussed in this unit. We will also learn how to convert binary to gray code and vice versa. In the next units, we will discuss about boolean algebra and logic gates.

#### 4.3 COMPUTER CODE

A **code** is a symbol or group of symbols that represents discrete elements. Coding of characters has been standardised to enable transfer of data between computers. *Numeric data* is not the only form of data handled by a computer. We often require to process *alphanumeric data*. An alphanumeric data is a string of symbols, where a symbol may be one of the letters A, B, C, ...., Z, or one of the digits 0, 1, 2, ...., 9, or a special character, such as + - \*/, . () = (space for blank) etc. However, the bits 0 and 1 must represent any data internally. Hence, computers use binary coding schemes to represent data internally. In binary coding, a group of bits represent every symbol that appears in the data. The group of bits used to represent a symbol is called a *byte*. To indicate the numbers of bits in a group, sometimes a byte is referred to as "n-bit byte", where the group contains n bits. However, the term "byte" commonly means an 8-bit byte because most modern computers use 8 bits to represent a symbol.

#### 4.4 BCD NUMBER

In computing and electronic systems, **Binary-Coded Decimal** (**BCD**) is a way to express each of the decimal digits with a binary code. Its main advantage is that it allows easy conversion to decimal digits for printing or display and faster decimal calculations. Decimal numbers with their BCD equivalent are given in the Table 4.1 :

| Decimal | BCD  |

|---------|------|

| 0       | 0000 |

| 1       | 0001 |

| 2       | 0010 |

| 3       | 0011 |

| 4       | 0100 |

| 5       | 0101 |

| 6       | 0110 |

| 7       | 0111 |

| 8       | 1000 |

| 9       | 1001 |

Table 4.1 : BCD Code

Unlike binary encoded numbers, BCD encoded numbers can easily be displayed by mapping each of the nibbles(4-bits) to a different character. Examples of conversion of decimal to BCD and BCD to decimal are included below:

**Example 4.1 :** Convert the decimal numbers 47 and 180 to BCD.

Solution :

4 = 0100 and 7 = 111

47 = 0100111

Similarly, 180=0001 1000 0000

**Example 4.2 :** Convert each of the BCD code 1000111 to decimal.

**Solution :** First we have to divide the whole BCD code by a set of 4-bits from right to left. Then from left to right we can put the corresponding decimal numbers.

0100 0111 4 7

Thus, 1000111(in BCD) = 47 (in Decimal)

**BCD addition :** BCD is a numeric code and can be used in arithmetic operations. Addition is the most important operation because the other three operations (subtraction, multiplication, and division) can be accomplished by the use of addition. Here is how to add two BCD numbers:

Step1 : Add the two BCD numbers, using the rules for binary addition.

Step 2 : If a 4-bit sum is equal to or less than 9, it is a valid BCD number.

Step 3 : If a 4-bit sum is greater than 9, or if a carry out of the 4-bit group is generated, it is an invalid result. Add 6(0110) to the 4-bit sum in order to skip the six invalid states and return the code to 8421. If a carry results when 6 is added, simply add the carry to the next 4-bit group.

Example 4.3 : Add the following BCD numbers :

a) 0001 + 0100

b) 10000111 + 01010011

Solution : The decimal number addition are shown for comparison.

| (a)  | 0001          | 1             |                           |

|------|---------------|---------------|---------------------------|

|      | <u>+0100</u>  | <u>+4</u>     |                           |

|      | 0101          | 5             |                           |

| .: O | 0001 + 0100 = | 0101 Which is | valid BCD no. (Value < 9) |

| (b)  | 1000          | 0111          | 87                        |

|      | <u>+0101</u>  | <u>0011</u>   | <u>+ 53</u>               |

1101

1010

Both groups are invalid (>9) +140

+0110

+0110

Add 6 (i.e.,0110) to both groups

0001

0100

0000

Valid BCD number which is 140 in decimal.

#### 4.5 ASCII CODE

ASCII stands for American Standard Code for Information Interchange. It is a very well-known fact that computers can manage internally only 0s (zeros) and 1s (ones). By means of sequences of 0s and 1s the computer can express any numerical value as its binary translation, which is a very simple mathematical operation.

However, there is no such evident way to represent letters and other non-numeric characters with 0s and 1s. Therefore, in order to do that, computers use *ASCII tables*, which are tables or lists that contain all the letters in the roman alphabet plus some additional characters. In these tables each character is always represented by the same order number. For example, the ASCII code for the capital letter "A" is always represented by the order number 65, which is easily representable using 0s and 1s in binary: 65 expressed as a binary number is 1000001. ASCII has 128 character codes(from 0 to 127) and symbols represented by a 7-bit binary code.

ASCII is the common code for microcomputer equipment. The first 32 characters in the ASCII-table are unprintable control codes and are used to control peripherals such as printers. Examples of control characters are "NULL", "line feed", "start of text" and "escape". The other characters are graphic symbols that can be printed or displayed and that include the letters of the alphabet (lowercase and upper case), the ten decimal digits, punctuation signs, and other commonly used symbols.

#### 4.6 EBCDIC

EBCDIC is the abbreviation for **Extended Binary-Coded Decimal Interchange Code**. EBCDIC is an IBM code for representing characters as numbers. It uses 8 bits per character. Thus 256 charaters can be represented with 8 bits. The 9th position bit can be used for parity. The EBCDIC code is used in IBM mainframe models and other similar machines. In EBCDIC, the first 4 bits are known as zone bits and remaining 4 bits represent digit values. Electronic circuits are available to transform characters from ASCII to EBCDIC and vice-varsa.

## 4.7 GRAY CODE

The gray code is an unweighted code not suited for arithmetic operations, but useful for input output devices, analog to digital converters etc. The **Gray code**, named after *Frank Gray*, is a binary numeral system where two successive values differ in only one digit. It is sometimes referred to as reflected binary, because the first eight values compare with those of the last 8 values, but in reverse order.

The Gray code was originally designed to prevent spurious output from electromechanical switches. Today, Gray codes are widely used to facilitate error correction in digital communications such as digital terrestrial television and some cable TV systems.

| Decimal | Gray Code | Binary |

|---------|-----------|--------|

| 0       | 0000      | 0000   |

| 1       | 0001      | 0001   |

| 2       | 0011      | 0010   |

| 3       | 0010      | 0011   |

| 4       | 0110      | 0100   |

| 5       | 0111      | 0101   |

| 6       | 0101      | 0110   |

| 7       | 0100      | 0111   |

| 8       | 1100      | 1000   |

| 9       | 1101      | 1001   |

| 10      | 1111      | 1010   |

| 11      | 1110      | 1011   |

| 12      | 1010      | 1100   |

| 13      | 1011      | 1101   |

| 14      | 1001      | 1110   |

| 15      | 1000      | 1111   |

Table 4.2 : Gray Code

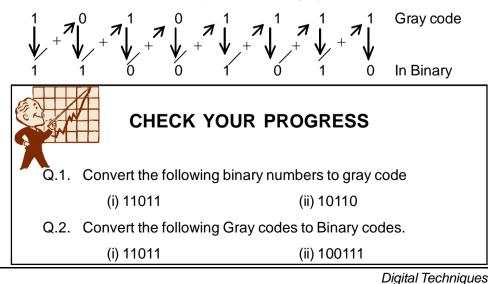

**Conversion from Binary to Gray code** : The following rules explain how to convert from a binary number to a Gray code :

a) The most significant bit (left most) in the gray code is the same as the corresponding most significant bit in the binary code.

b) Going from left to right, add each pair of adjacent pair of binary code to get the next Gray code bit. Discard carries.

For example, the conversion of the binary number 1100 to gray code is as follows:

Binary code 1 1 0 0

MSB (Most significant bit) LSB (Least significant bit)

MSB of Gray code will be same as MSB of Binary code. Here, it will be 1. Now, addition of each pair of adjacent bits of Binary code:

1 + 1 = 10 = 0, discarding the carry 1

1 + 0 = 1, no carry

0 + 0 = 0, no carry

Therefore, 1100 in gray code is 1010

Conversion from Gray to Binary code : The following rules apply:

a) The most significant bit (left most) in the binary code is the same as the corresponding most significant bit in the gray code.

b) Add each binary code bit generated by Gray code bit in the next adjacent position. Discard carries.

For example, binary 10101111 in gray code will be like this :

- Q.3. (i) The American Standard Code for Information Interchange is a standard \_\_\_\_\_\_ bits code.

- (ii) EBCDIC uses \_\_\_\_\_ bits per character.

- (iii) Code is a representation of \_\_\_\_\_.

- (iv) In both binary and gray code, the \_\_\_\_\_\_ is same.

- Q.4. Add the following BCD numbers : (i) 00100011 + 00010001 (ii) 1001 + 0100

# 4.8 LET US SUM UP

- I BCD code is a way to express decimal digits with a binary code.

- I BCD, ASCII, EBCDIC, and Gray Code are the commonly used commputer codes.

- I BCD is a numeric code and can be used in arithmetic operations.

- I ASCII is a 7 bit binary code.

- I EBCDIC uses 8-bits to represent character.

- I Gray codes are used to facilitate error correction.

- ASCII stands for American Standard Code for Information Interchange.

- I Gray codes area not not suited for arithmetic operations.

## 4.9 FURTHER READING

- Ram, B. (2000), Computer Fundamentals Architecture and Organization, New Age International

- I Mano, M.M. (2017), Digital Logic and Computer Design, Pearson Education India

- I Sinha, P. K. and Sinha P. (2010), Computer Fundamentals, BPB Publication.

- I Talukdar, P. (2010), Digital Techniques, N.L. Publications.

# 4.10 ANSWERS TO CHECK YOUR PROGRESS

| Ans. to Q. No. 1 : | (i) 10110     | (ii) 11101                             |

|--------------------|---------------|----------------------------------------|

| Ans. to Q. No. 2 : | (i) 10010     | (ii) 111010                            |

| Ans. to Q. No. 3 : | (i) 7         | (ii) 8 (iii) Discrete elements         |

|                    | (iv) MSB-b    | it                                     |

| Ans. to Q. No. 4 : | (i) Solution  | 1:                                     |

|                    | 0010          | 0011 35                                |

|                    | +0001         | <u>0001</u> <u>+17</u>                 |

|                    | 0011          | 0100 +52 Valid BCD no. (since both <9) |

|                    | (ii) Solutior | n:                                     |

|                    | 1001          | 9                                      |

|                    | <u>+0100</u>  | <u>+4</u>                              |

|                    | 1101          | Invalid BCD number (>9) +13            |

|                    | <u>+0110</u>  | Add 6 (i.e., 0110)                     |

| 00                 | 001 0011      | A valid BCD number which               |

|                    |               | is 13 in decimal                       |

## 4.11 MODEL QUESTIONS

- Q1. What is BCD code?

- Q2. Convert the decimal numbers 15, 275 to BCD.

- Q3. Add the two BCD numbers 10000111 and 01010011.

- Q4. Write BCD for the following decimal number:

(i) 679 (ii) 45.96

- Q.5. Give the importance of Gray codes.

- Q.6. Write a short note on ASCII codes.

\*\*\*\*\*\*

## **UNIT 5 : BOOLEAN ALGEBRA**

## UNIT STRUCTURE

- 5.1 Learning Objectives

- 5.2 Introduction

- 5.3 Boolean Operators

- 5.4 Basic Theorems and Postulates of Boolean Algebra

- 5.5 Let Us Sum Up

- 5.6 Further Reading

- 5.7 Answers to Check Your Progress

- 5.8 Model Questions

## 5.1 LEARNING OBJECTIVES

After going through this unit, you will be able to :

- I define Boolean algebra

- I explain basic concepts of Boolean Algebra

- I define the basic theorems and postulates of Boolean Algebra

- I define Boolean function

## 5.2 INTRODUCTION

In the previous units we have been introduced to concepts like binary arithmetic, data representation and code conversion. We have learnt about the methods for representing data. We have also learnt about the different types of computer codes like gray, BCD, ASCII and EBCDIC codes. The conversion process from one code to another is also discussed in previous units.

In this unit, you will be able to learn about the fundamentals of Boolean Algebra. You will also learn the basic theorems and postulates of Boolean algebra. Different concepts like the principles of Duality, De Morgan's theorem are also covered in this unit.

In the next unit, we will learn about the different types of logic gates. Conversion of logic gates is also covered in the next unit.

#### 5.3 BOOLEAN OPERATORS

Boolean algebra may be defined with the help of three sets of components viz,

- i) a set of elements,

- ii) a set of operators and

- iii) a number of unproved axioms or postulates.

A set of elements is any collection of objects having a common property. A set of operators are the binary operators, which are rules that are assigned to each pair of elements of the set, a unique element from the set. The axioms or postulates form the basic assumptions from which it is possible to deduce the rules, theorems and properties of Boolean algebra. A variable in Boolean algebra can take only two vales, 1 (TRUE) or 0 (FALSE). i.e. TRUE is represented by 1 and FALSE is represented by 0. Boolean algebra is used for designing and analysing digital circuits. There are three basic operations in Boolean algebra and these operations are done with the help of three operators, viz. AND, OR and NOT. (These are also called basic logic operation).

**AND operation :** Boolean AND operator for two variables A and B can be represented as:

A and B or A.B or AB

It results 1 or TRUE if both the operands A and B are 1 (TRUE), otherwise the result is 0 (FALSE).

**OR Operation :** The OR operator for the same variables can be represented as :

A OR B or A+B

The result of this operation in 0 (FALSE) if both the variables are 0 (FALSE); otherwise the result is 1 (TRUE).

**NOT Operation :** The NOT operation for a variable A can be represented as:

NOT  $\overline{A}$  or A or A<sup>/</sup>.

It returns the opposite value of the variable i.e. returns 0 (FALSE) if A is 1 (TRUE) and vice versa.

The results of these Boolean operations can be represented in a tabular form, which is referred to as the "*truth table*".

| Α | В | (A AND B) A.B | (A OR B) A+B | NOT(A) |

|---|---|---------------|--------------|--------|

| 0 | 0 | 0             | 0            | 1      |

| 0 | 1 | 0             | 1            | 1      |

| 1 | 0 | 0             | 1            | 0      |

| 1 | 1 | 1             | 1            | 0      |

Table 5.1: Truth Table for AND, OR and NOT operation

**Note :** Boolean addition is same as the OR operation and Boolean multiplication is same as AND operation.

**Truth Table :** A truth table is a table which gives the output for all combination of input values. A truth table can be drawn for a particular function/operation. In the truth Table 5.1, three tables are merged into a single one.

In addition to these three basic Boolean operations, three more operators have been defined for Boolean algebra. They are: XOR (Exclusive OR), NOR (Not+OR) and NAND (Not+AND).

# 5.4 BASIC THEOREMS AND POSTULATES OF BOOLEAN ALGEBRA

The theorems and postulates are the most basic relationships in Boolean algebra. Six theorems and four postulates of Boolean algebra are listed in Table 5.2. The postulates are basic axioms of the algebric structure and need no proof, but the theorems must be proven with the help of the postulates. Both the postulates and theorems are listed in pairs: one is the dual of the other.

#### Table 5.2 Postulates and Theorems of Boolean Algebra

| Postulate 2    | (a) x + 0 = z    | (b) x.1 = x                       |

|----------------|------------------|-----------------------------------|

| Postulate 5    | (a) x + x′ = 1   | (b) x. $x' = 0$                   |

| Theorem 1      | (a) x + x = x    | (b) x. x = x                      |

| Theorem 2      | (a) x + 1 = 1    | (b) x. 0 = 0                      |

| Theorem 3, Ir  | nvolution (x') / | =x                                |

| Postulate 3, 0 | Commutative      | (a) $x + y = y + x$ (b) $xy = yx$ |

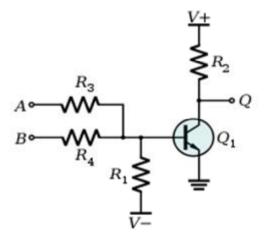

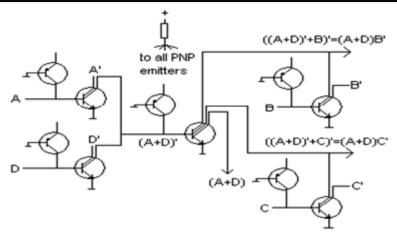

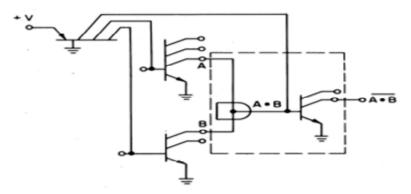

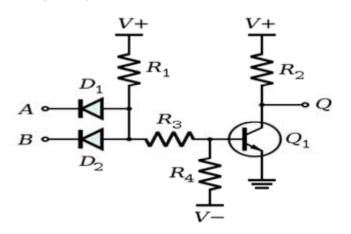

| Theorem 4, A   | ssociative       | (a) $x + (y + z) = (x + y) + z$   |