## अखिल भारतीय तकनीकी शिक्षा परिषद् All India Council for Technical Education

## **Basics of Electronics**

## **Brijesh** lyer

II Year Degree level book as per AICTE model curriculum (Based upon Outcome Based Education as per National Education Policy 2020). The book is reviewed by Dr. Sanjay L. Nalbalwar

## **BASIC OF ELECTRONICS**

Authored By

Dr. Brijesh lyer

Assistant Professor (Sel. Gr.) Department of E & TC Engineering Dr. Babasaheb Ambedkar Technological University, Lonere Lonere, Maharashtra (India)

**Reviewed By**

## Dr. Sanjay Nalbalwar

Professor & Head Department of E & TC Engineering Dr. Babasaheb Ambedkar Technological University, Lonere Lonere, Maharashtra (India)

## **All India Council for Technical Education**

Nelson Mandela Marg, Vasant Kunj,

New Delhi, 110070

#### **BOOK AUTHOR DETAILS**

Dr. Brijesh Iyer, Assistant Professor (Sel. Gr.), Department of E & TC Engineering, Dr. Babasaheb Ambedkar Technological University, Lonere, Maharashtra (India) Email ID: <u>brijeshiyer@dbatu.ac.in</u>

#### **BOOK REVIEWER DETAILS**

Dr. Sanjay Nalbalwar, Professor & Head, Department of E & TC Engineering, Dr. Babasaheb Ambedkar Technological University, Lonere, Maharashtra (India) Email ID: <u>slnalbalwar@dbatu.ac.in</u>

#### BOOK COORDINATOR (S) – English Version

- Dr. Ramesh Unnikrishnan, Advisor-II, Training and Learning Bureau, All India Council for Technical Education (AICTE), New Delhi, India Email ID: <u>advtlb@aicte-india.org</u> Phone Number: 011-29581215

- Dr. Sunil Luthra, Director, Training and Learning Bureau, All India Council for Technical Education (AICTE), New Delhi, India Email ID: <u>directortlb@aicte-india.org</u> Phone Number: 011-29581210

- Mr. Sanjoy Das, Assistant Director, Training and Learning Bureau, All India Council for Technical Education (AICTE), New Delhi, India Email ID: <u>ad1tlb@aicte-india.org</u> Phone Number: 011-29581339

#### July, 2023

© All India Council for Technical Education (AICTE)

#### **ISBN :** 978-81-963773-2-8

## All rights reserved. No part of this work may be reproduced in any form, by mimeograph or any other means, without permission in writing from the All India Council for Technical Education (AICTE).

Further information about All India Council for Technical Education (AICTE) courses may be obtained from the Council Office at Nelson Mandela Marg, Vasant Kunj, New Delhi-110070.

Printed and published by All India Council for Technical Education (AICTE), New Delhi.

## Attribution-Non Commercial-Share Alike 4.0 International (CC BY-NC-SA 4.0)

**Disclaimer:** The website links provided by the author in this book are placed for informational, educational & reference purpose only. The Publisher do not endorse these website links or the views of the speaker / content of the said weblinks. In case of any dispute, all legal matters to be settled under Delhi Jurisdiction, only.

अखिल भारतीय तकनीकी शिक्षा परिषद् (शास लखार का एक संप्रियेक निकाय) (रिक्रा मंत्रालय, सारा लखार) नेलन संदेश का जुंब, चं रेल्ले-11000 दूल्या 1 011-2613/लह इं-नेल : cteaman@acte-india.org ALL INDIA COUNCIL FOR TECHNICAL EDUCATION

आजादी न अमत महोत्सव (A STATUTORY SOLY OF THE GOVE OF MOA) (Mnisry of Education, Gove of mola) (Mnisry of Education, Gove of India) Nelson Mandels Marg, Vasant Kunj, New Delhi-110070 Phone : 011-26131498 E-mail : chairman@acte-india.org

#### FOREWORD

Engineers are the backbone of any modern society. They are the ones responsible for the marvels as well as the improved quality of life across the world. Engineers have driven humanity towards greater heights in a more evolved and unprecedented manner.

The All India Council for Technical Education (AICTE), have spared no efforts towards the strengthening of the technical education in the country. AICTE is always committed towards promoting quality Technical Education to make India a modern developed nation emphasizing on the overall welfare of mankind.

An array of initiatives has been taken by AICTE in last decade which have been accelerated now by the National Education Policy (NEP) 2020. The implementation of NEP under the visionary leadership of Hon'ble Prime Minister of India envisages the provision for education in regional languages to all, thereby ensuring that every graduate becomes competent enough and is in a position to contribute towards the national growth and development through innovation & entrepreneurship.

One of the spheres where AICTE had been relentlessly working since past couple of years is providing high quality original technical contents at Under Graduate & Diploma level prepared and translated by eminent educators in various Indian languages to its aspirants. For students pursuing 2<sup>rd</sup> year of their Engineering education, AICTE has identified 88 books, which shall be translated into 12 Indian languages - Hindi, Tamil, Gujarati, Odia, Bengali, Kannada, Urdu, Punjabi, Telugu, Marathi, Assamese & Malayalam. In addition to the English medium, books in different Indian Languages are going to support the students to understand the concepts in their respective mother tongue.

On behalf of AICTE, I express sincere gratitude to all distinguished authors, reviewers and translators from the renowned institutions of high repute for their admirable contribution in a record span of time.

AICTE is confident that these outcomes based original contents shall help aspirants to master the subject with comprehension and greater ease.

Prof. T. G. Sitharam)

## ACKNOWLEDGEMENT

The author is grateful to the authorities of AICTE, particularly Prof. T.G. Sitharam, Chairman; Dr. Abhay Jere, Vice-Chairman; Prof. Rajiv Kumar, Member-Secretary, Dr. Ramesh Unnikrishnan, Advisor-II and Dr. Sunil Luthra, Director, Training and Learning Bureau for their planning to publish the books on *Basic of Electronics*.

I would like to express my sincere appreciation to Dr. Sanjay Nalbalwar, Professor & Head of the Department of E&TC Engineering at Dr. Babasaheb Ambedkar Technological University, Lonere-402103(MS)-India, for his contributions as a book reviewer. His efforts have made the book more accessible to students and have given it an artistic touch, resulting in a better overall shape.

I am deeply grateful to my wife, Dr. Prachi, and my children, Ku. Rajnandini and Chi. Prabhasdatt, for their unwavering patience throughout the completion of this project. Without their support, this work would not have come to fruition.

I would also like to acknowledge the reference books that have been instrumental in the preparation of this book: "Electronic Devices and Circuit Theory" by Robert Boylestad and Louis Nashelsky, "Digital Fundamentals" by Thomas Floyd, "Electronic Instrumentation and Measurements" by David Bell, and "A Course In Electrical and Electronic Measurements and Instrumentation" by A.K. Sawhney. Additionally, I extend my gratitude to Mr. Dixit Jain of Synergy Books Pvt. Ltd. Mumbai for his initial support and motivation.

Over the years, my students have made significant contributions that have enriched my experience and expertise in this subject. I am immensely grateful for their valuable input.

This book is the result of various suggestions provided by members of the All India Council for Technical Education (AICTE), experts, and authors who have shared their opinions and thoughts on advancing engineering education in our country. I extend my heartfelt acknowledgment to these contributors and all the individuals working in this field whose published books, review articles, papers, photographs, footnotes, references, and other valuable information have enriched our work during the writing process.

Dr. Brijesh Iyer

## PREFACE

I take great pleasure in introducing the textbook "Basic of Electronics," which is the culmination of my extensive experience in teaching fundamental courses in electronics engineering. The motivation behind writing this book is to provide engineering students with a comprehensive understanding of the basic concepts and fundamentals of electronics engineering, allowing them to gain insight into the subject. With a focus on broad coverage and essential supplementary information, the book incorporates topics recommended by the All India Council for Technical Education (AICTE) in a systematic and organized manner. Special effort has been made to explain the fundamental concepts in the simplest possible way.

Throughout the preparation process, I extensively referred to various standard textbooks and developed sections such as critical questions, solved and supplementary problems, and more. Emphasis has been placed on definitions, laws, and comprehensive synopses of formulas for quick revision of the basic principles. The book addresses a wide range of medium and advanced-level problems, presented in a logical and systematic manner. These problem gradations have been tested over many years of teaching, catering to diverse student backgrounds.

In addition to relevant illustrations and examples, the book is enriched with solved problems in each unit to facilitate a comprehensive understanding of the topics. Each chapter is accompanied by solved examples, exercise questions, self-study questions, and multiple-choice questions.

I sincerely hope that this book will inspire students to delve into and discuss the underlying ideas behind the basic principles of electronics engineering. It aims to establish a solid foundation in the subject matter. I welcome and appreciate all valuable comments and suggestions that will contribute to the enhancement of future editions of this book. It is my utmost pleasure to present this book to both teachers and students. Working on the various aspects covered in this book has been a truly gratifying experience.

Dr. Brijesh Iyer

## OUTCOME BASED EDUCATION

For the implementation of an outcome-based education, the first requirement is to develop an outcomebased curriculum and incorporate an outcome-based assessment in the education system. By going through outcome-based assessments evaluators will be able to evaluate whether the students have achieved the outlined standard, specific and measurable outcomes. With the proper incorporation of outcome-based education, there will be a definite commitment to achieve a minimum standard for all learners without giving up at any level. At the end of the program running with the aid of outcome-based education, a student will be able to arrive at the following outcomes:

- **PO1.** Engineering knowledge: Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

- **PO2. Problem analysis**: Identity, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using the first principles of mathematics, natural sciences, and engineering sciences.

- **PO3.** Design/development of solutions: Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for public health and safety, and cultural, societal, and environmental considerations.

- **PO4.** Conduct investigations of complex problems: Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

- **PO5.** Modern tool usage: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

- **PO6.** The engineer and society: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

- **PO7.** Environment and sustainability: Understand the impact of professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

- **PO8.** Ethics: Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

- **PO9.** Individual and team work: Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

- **PO10.** Communication: Communicate effectively on complex engineering activities with the engineering community and with society at large, such as being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

- **PO11. Project management and finance**: Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

- **PO12.** Life-long learning: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

## **COURSE OUTCOMES**

After completion of the course, the students will be able to:

- CO-1: Apply basic ideas and principles of Electronics Engineering

- CO-2: To study of PN Junction devices and its applications

- CO-3: To study the construction, working of a transistor and apply its characteristics

- CO-4: To understand the concept of feedback amplifiers and oscillators

- CO-5: To know the fundamentals of Op-Amp its applications

CO-6: To understand the working principles of various measuring instruments and transducers

CO-7: To acquire the fundamental concepts of digital electronics.

| Course<br>Outcomes |      |      | (1- Weak | -    | -    |      | <b>ith Prog</b> i<br>Im correl |      |      |       | ation) |       |

|--------------------|------|------|----------|------|------|------|--------------------------------|------|------|-------|--------|-------|

| Outcomes           | PO-1 | PO-2 | PO-3     | PO-4 | PO-5 | PO-6 | PO-7                           | PO-8 | PO-9 | PO-10 | PO-11  | PO-12 |

| CO-1               | 3    | 3    | 2        | 1    | -    | 1    | -                              | -    | -    | -     | -      | 1     |

| CO-2               | 3    | 3    | 2        | 1    | -    | -    | -                              | -    | -    | -     | -      | -     |

| CO-3               | 3    | 3    | 2        | 1    | -    | -    | -                              | -    | -    | -     | -      | -     |

| CO-4               | 3    | 3    | 3        | 2    | -    | -    | -                              | -    | -    | -     | -      | -     |

| CO-5               | 3    | 3    | 3        | 1    | -    | -    | -                              | -    | -    | -     | -      | -     |

| CO-6               | 3    | 3    | 2        | 2    | -    | -    | -                              | -    | -    | -     | -      | -     |

| CO-7               | 3    | 3    | 3        | 1    | -    | 1    | -                              | -    | -    | -     | -      | -     |

## **GUIDELINES FOR TEACHERS**

To implement Outcome Based Education (OBE) knowledge level and skill set of the students should be enhanced. Teachers should take major responsibility for the proper implementation of OBE. Some of the responsibilities (not limited to) for the teachers in the OBE system may be as follows:

- Within reasonable constraints, they should manoeuvre the time to the best advantage of all students.

- They should assess the students only upon certain defined criteria without considering any other potential ineligibility to discriminate against them.

- They should try to grow the learning abilities of the students to a certain level before they leave the institute.

- They should try to ensure that all the students are equipped with quality knowledge as well as competence after they finish their education.

- They should always encourage the students to develop their ultimate performance capabilities.

- They should facilitate and encourage group work and teamwork to consolidate newer approaches.

- They should follow Blooms taxonomy in every part of the assessment.

|         | Level      |                                     | Teacher should<br>Check                   | Students should be able to | Possible Mode of<br>Assessment           |

|---------|------------|-------------------------------------|-------------------------------------------|----------------------------|------------------------------------------|

|         | Create     |                                     | Student's ability to create               | Design or Create           | Mini project                             |

|         | Evaluate   |                                     | Student's ability to<br>justify           | Argue or Defend            | Assignment                               |

| Analyse |            | Student's ability to<br>distinguish | Differentiate or<br>Distinguish           | Project/Lab<br>Methodology |                                          |

|         | Apply      |                                     | Student's ability to use information      | Operate or<br>Demonstrate  | Technical Presentation/<br>Demonstration |

|         | Understand |                                     | Student's ability to explain the ideas    | Explain or Classify        | Presentation/Seminar                     |

|         | Remember   |                                     | Student's ability to recall (or remember) | Define or Recall           | Quiz                                     |

## **Bloom's Taxonomy**

## **GUIDELINES FOR STUDENTS**

Students should take equal responsibility for implementing the OBE. Some of the responsibilities (not limited to) for the students in the OBE system are as follows:

- Students should be well aware of each UO before the start of a unit in every course.

- Students should be well aware of each CO before the start of the course.

- Students should be well aware of each PO before the start of the program.

- Students should think critically and reasonably with proper reflection and action.

- The learning of the students should be connected and integrated with practical and real-life consequences.

- Students should be well aware of their competency at every level of OBE.

## ABBREVIATIONS AND SYMBOLS

## List of Abbreviations

|               | General Terms                                                       |               |                                                      |  |  |

|---------------|---------------------------------------------------------------------|---------------|------------------------------------------------------|--|--|

| Abbreviations | Full form                                                           | Abbreviations | Full form                                            |  |  |

| AC            | Alternative Current                                                 | HWR           | Half Wave Rectifier                                  |  |  |

| ASIC          | Application-Specific Integrated<br>Circuits                         | JFET          | Junction Field Effect Transistor                     |  |  |

| BCD           | Binary Coded Decimal                                                | LED           | Light Emitting Diode                                 |  |  |

| BJT           | Bipolar Junction Transistor                                         | LSB           | Least Significant Bit                                |  |  |

| СВ            | Common Base Configuration                                           | LVDT          | Linear Variable Differential<br>Transformer          |  |  |

| CC            | Common Collector<br>Configuration                                   | MOSFET        | Metal Oxide Semiconductor<br>Field Effect Transistor |  |  |

| CD            | Diffusion Capacitance                                               | MSB           | Most Significant Bit                                 |  |  |

| CE            | Common Emitter<br>Configuration                                     | PIV           | Peek Inverse Voltage                                 |  |  |

| CMOS          | Complementary Metal Oxide<br>Semiconductor                          | РММС          | Permanent Magnet Moving<br>Coil                      |  |  |

| CMRR          | Common Mode Rejection<br>Ratio                                      | RAM           | Random Access Memory                                 |  |  |

| D- MOSFET     | Depletion Metal Oxide<br>Semiconductor Field Effect<br>Transistor   | RMS           | Root Mean Square                                     |  |  |

| DC            | Direct Current                                                      | ROM           | Read Only Memory                                     |  |  |

| E- MOSFET     | Enhancement Metal Oxide<br>Semiconductor Field Effect<br>Transistor | SCR           | Silicon Controlled Rectifiers                        |  |  |

| EEPROM        | Electrically Erasable<br>Programmable Read Only<br>Memory           | SVRR          | Supply Voltage Rejection Ratio                       |  |  |

| FET           | Field Effect Transistor                                             | VLSI          | Very Large Scale Integration                         |  |  |

| Symbols          | Description               | Symbols          | Description                  |

|------------------|---------------------------|------------------|------------------------------|

| R <sub>D</sub>   | Static Resistance         | μ                | Amplification Factor         |

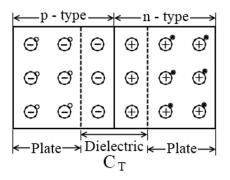

| $C_T$            | Transition Capacitance    | I <sub>GSS</sub> | Gate Cut-Off Current         |

| $C_D$            | Diffusion or storage      | $R_{GS}$         | Input Resistance             |

|                  | Capacitance               |                  |                              |

| η                | The Ratio or Efficiency   | $g_m$            | Trans-Conductance            |

| $R_Z$            | Zener Resistance          | $A_f$            | Feedback Amplifier           |

| $V_Z$            | Zener Voltage             | $V_s$            | Signal Voltage               |

| $P_Z$ max        | Maximum Power Dissipation | $I_s$            | Signal Current               |

| $I_Z$            | Zener Current             | I <sub>io</sub>  | Input Offset Current         |

| I <sub>C</sub>   | Collector Current         | $I_B$            | Input Bias Current           |

| $I_E$            | Emitter Current           | А                | Large Signal Voltage Gain    |

| S                | Stability Factor          | V <sub>CM</sub>  | Common Mode Voltage          |

| S' & S''         | Thermal Stability Factor  | V <sub>oo</sub>  | Output Offset Voltage        |

| I <sub>DSS</sub> | Drain to Source Current   | Vio              | Input Offset Voltage         |

| $V_{GS}$         | Gate to Source Voltage    | $R_T$            | Resistance of the Thermistor |

| $R_{DS}$         | Drain Source Resistance   | $G_f$            | Gauge Factors                |

## List of Symbols

## LIST OF FIGURES

## Unit 1 Diode and Its Application

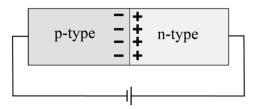

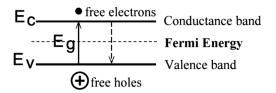

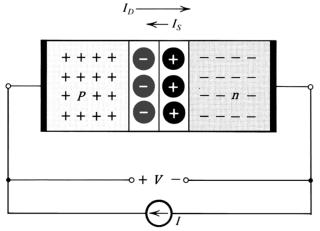

| Fig. 1.1 : P-N Junction with No bias condition                                               | 3  |

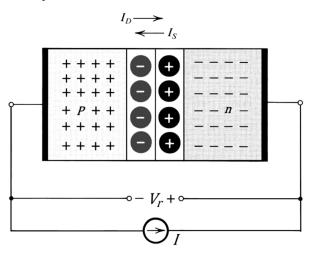

|----------------------------------------------------------------------------------------------|----|

| Fig. 1.2 : P-N Junction in reverse bias                                                      | 4  |

| Fig. 1.3 : P-N Junction in forward bias                                                      | 4  |

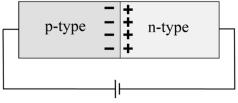

| Fig. 1.4 : The diode V-I characteristics                                                     | 4  |

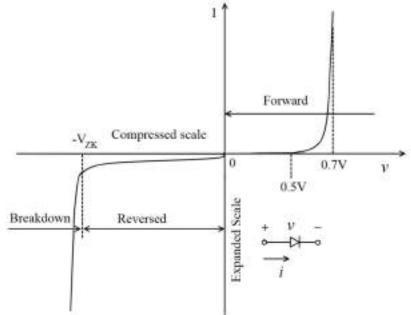

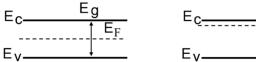

| Fig. 1.5 : Basic structure of energy band diagram in semiconductor                           | 5  |

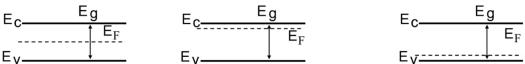

| Fig. 1.6 : Fermi level position in doped semiconductors                                      | 5  |

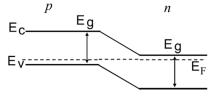

| Fig. 1.7 : Band diagram before contact                                                       | 5  |

| Fig. 1.8 : Band diagram after contact(Ideal case)                                            | 6  |

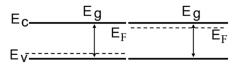

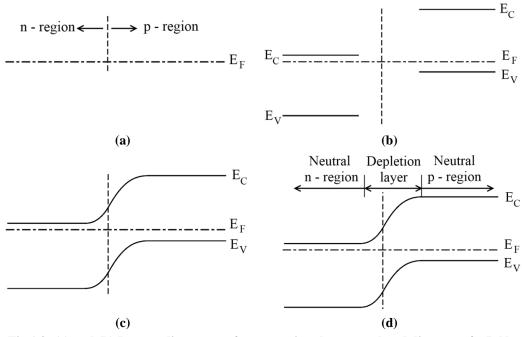

| Fig. 1.9 : (a) and (b) Intermediate steps of constructing the energy band diagram of a P-N   | 6  |

| junction, (c) and (d) The complete band diagram                                              |    |

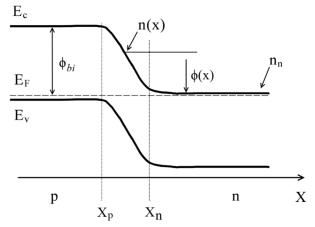

| Fig. 1.10 : Practical energy band diagram for a P-N junction                                 | 7  |

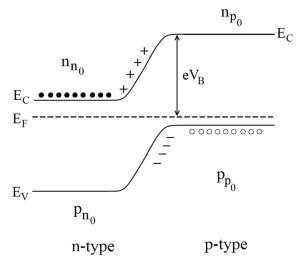

| Fig. 1.11 : Energy band diagram under thermal equilibrium                                    | 8  |

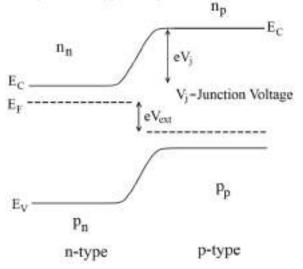

| Fig. 1.12 : Energy band diagram under external bias                                          | 8  |

| Fig. 1.13 : P-N Junction in forward bias                                                     | 9  |

| Fig. 1.14 : P-N Junction with reverse bias                                                   | 10 |

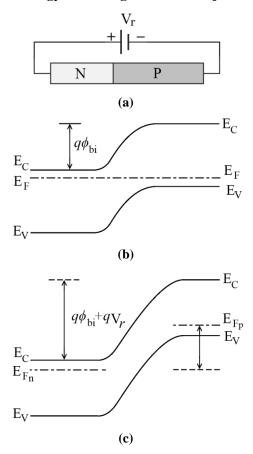

| Fig. 1.15 : (a) A reverse-biased P-N junction, (b) band diagram without bias, and (c) energy | 11 |

| band under reverse bias                                                                      |    |

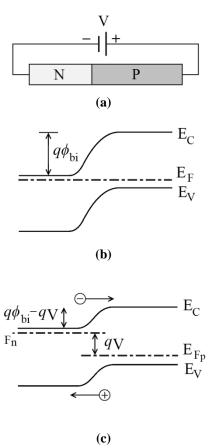

| Fig. 1.16: (a) A forward-biased P-N junction, (b) band diagram without bias, and (c) energy  | 11 |

| band under forward bias                                                                      |    |

| Fig. 1.17 : Depletion layer capacitance                                                      | 12 |

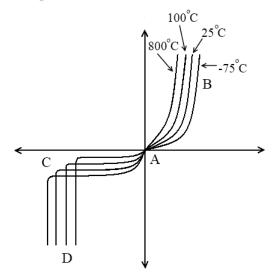

| Fig. 1.18 : Diode characteristics for different temperatures                                 | 14 |

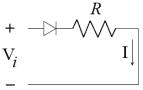

| Fig. 1.19 : A diode circuit                                                                  | 15 |

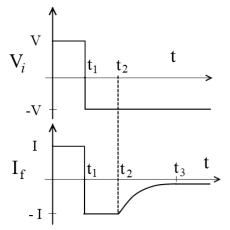

| Fig. 1.20 : Switching timing of diode                                                        | 16 |

| Fig. 1.21 : Storage timing of diode                                                                | 16 |

|----------------------------------------------------------------------------------------------------|----|

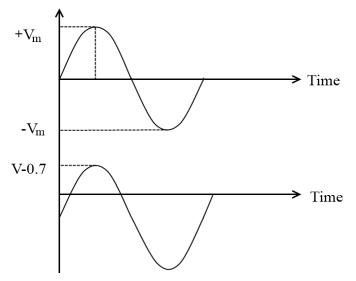

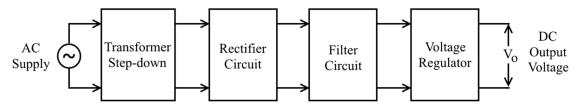

| Fig. 1.22 : Block diagram of DC power supply                                                       | 17 |

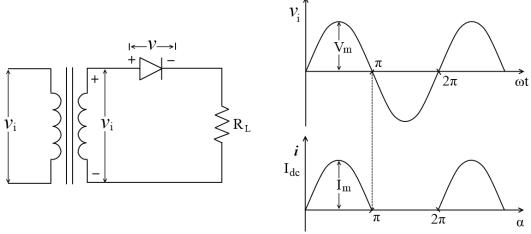

| Fig. 1.23 : Half Wave Rectifier circuit and its output waveform                                    | 17 |

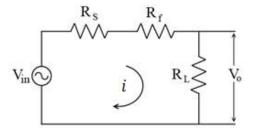

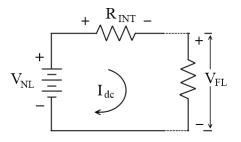

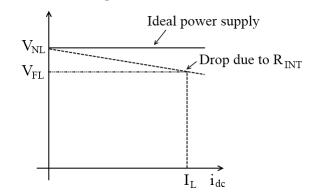

| Fig. 1.24 (a) : Thevenin's equivalent of Half wave rectifier                                       | 20 |

| Fig. 1.24 (b) : Variation in terminal voltage with load current for ideal & practical power supply | 20 |

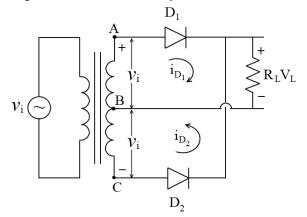

| Fig. 1.25 : A Centertap Full Wave Rectifier Circuit                                                | 22 |

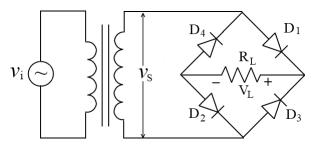

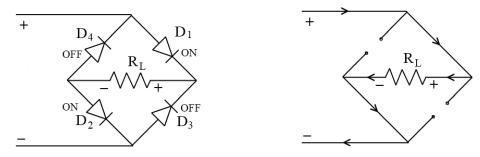

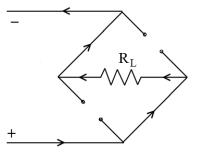

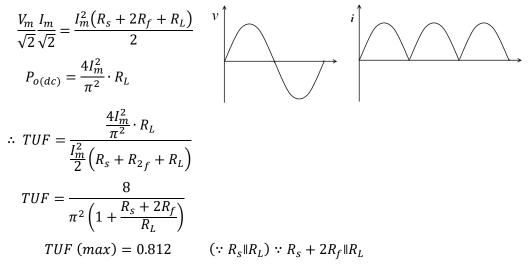

| Fig. 1.26 : Full Wave Bridge Rectifier Circuit                                                     | 25 |

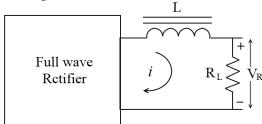

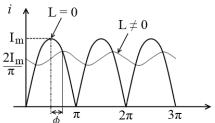

| Fig. 1.26(a) : Inductor filter circuit                                                             | 27 |

| Fig. 1.26(b) : Output of inductor filter                                                           | 27 |

| Fig. 1.27 : Output waveform of an inductor filter                                                  | 29 |

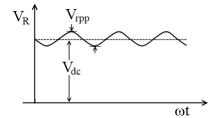

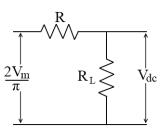

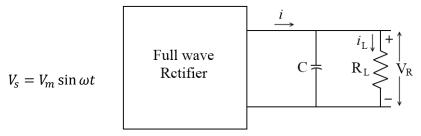

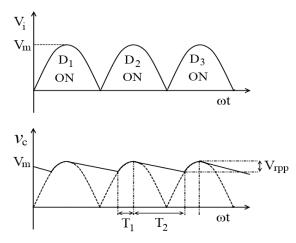

| Fig. 1.28 : Capacitor filter circuit                                                               | 29 |

| Fig. 1.29 : Output of capacitor filter                                                             | 30 |

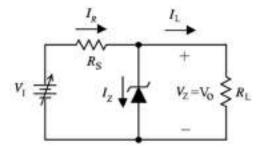

| Fig. 1.30 : Zener diode as a voltage regulator                                                     | 31 |

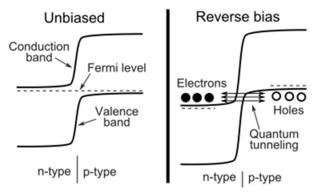

| Fig. 1.31 : Band diagram of Zener breakdown                                                        | 33 |

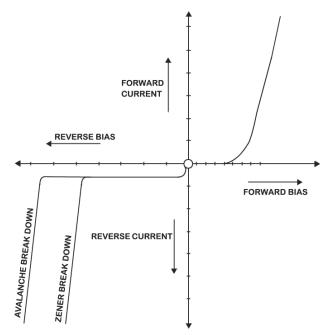

| Fig. 1.32 : I-V characteristics of Zener and Avalanche Breakdown                                   | 34 |

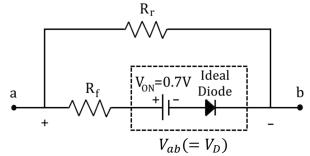

| Fig. 1.33 : A practical diode under DC operating conditions                                        | 35 |

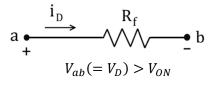

| Fig. 1.34(a) : Forward biased DC diode model                                                       | 35 |

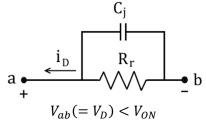

| Fig. 1.34(b) : Reverse biased DC diode model                                                       | 35 |

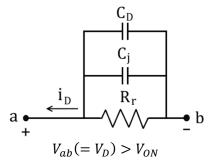

| Fig. 1.35 : Reverse biased ac diode model                                                          | 36 |

| Fig. 1.36 : Forward biased ac diode model                                                          | 36 |

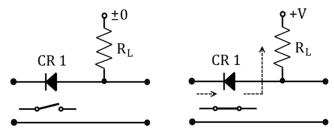

| Fig. 1.37 : Diode as a switch                                                                      | 37 |

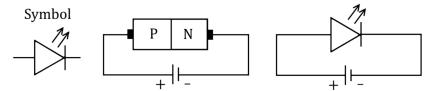

| Fig. 1.38 : Symbol and circuit diagram of a LED                                                    | 37 |

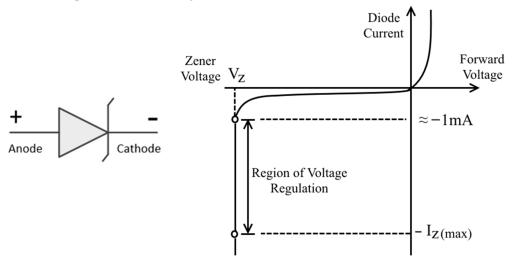

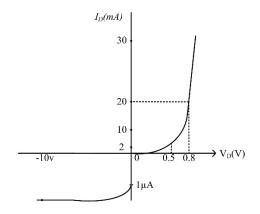

| Fig. 1.39 : Symbol and I-V Characteristics of a Zener diode                                        | 38 |

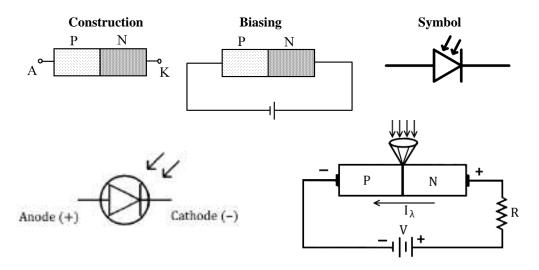

| Fig. 1.40 : The details of a photo diode                                                           | 39 |

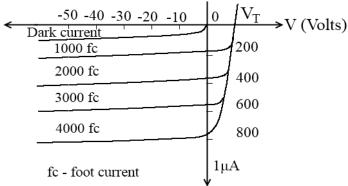

| Fig. 1.41 : V-I Characteristics of a photo diode                                                   | 39 |

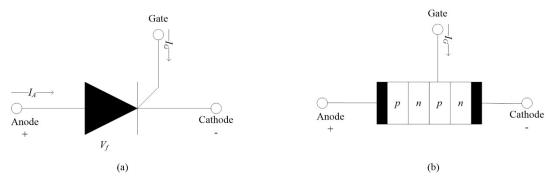

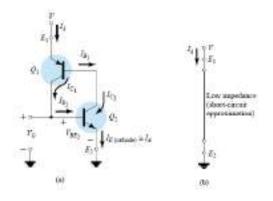

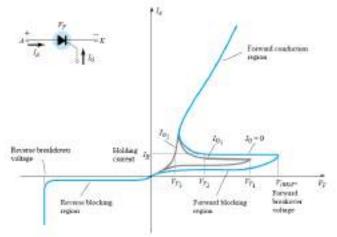

| Fig. 1.42 : (a) SCR symbol; (b) basic construction                                                 | 40 |

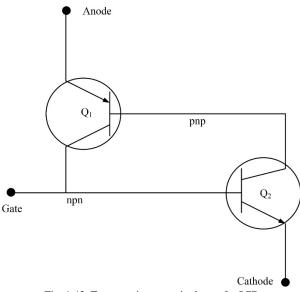

| Fig. 1.43 : Two transistor terminology of a SCR | 41 |

|-------------------------------------------------|----|

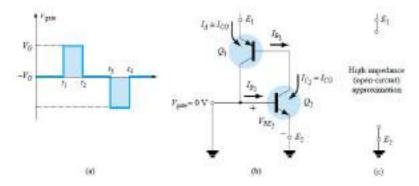

| Fig. 1.44 : "Off" state of the SCR              | 41 |

| Fig. 1.45 : "On" state of the SCR               | 42 |

| Fig. 1.46 : SCR characteristics                 | 42 |

## Unit 2 Transistor Characteristics

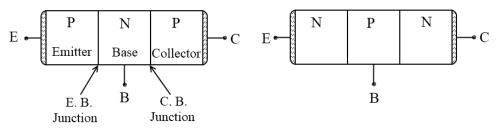

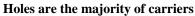

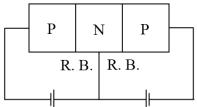

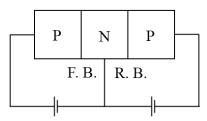

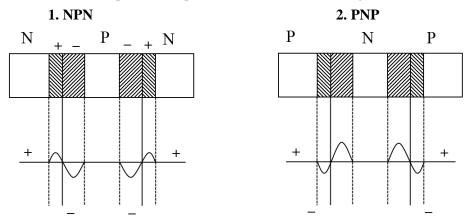

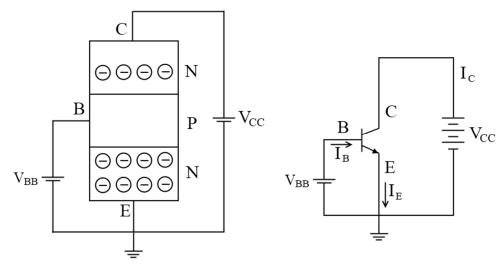

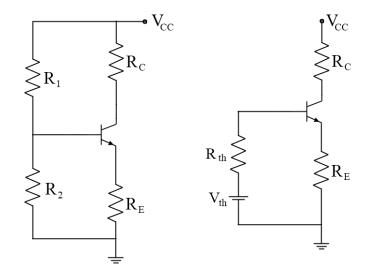

| Fig. 2.1 : Construction of BJT-PNP & NPN                                        | 53 |

|---------------------------------------------------------------------------------|----|

| Fig. 2.2 : Depletion Region and Barrier Potential                               | 55 |

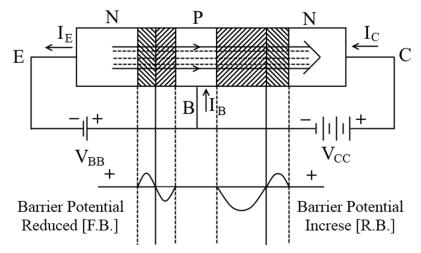

| Fig. 2.3 : Transistor Operation (NPN)                                           | 56 |

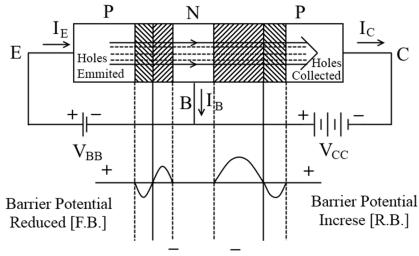

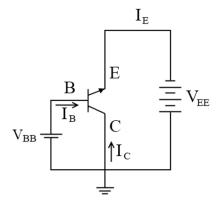

| Fig. 2.4 : Transistor Operation (PNP)                                           | 57 |

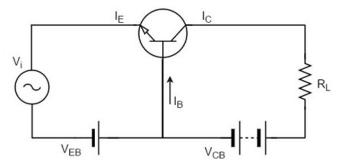

| Fig. 2.5 : Common Base Configuration                                            | 57 |

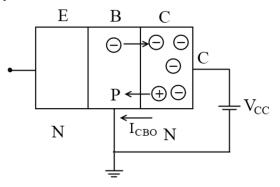

| Fig. 2.6 : I <sub>CBO</sub> In CB Configuration                                 | 58 |

| Fig. 2.7 : Common Emitter Configuration                                         | 58 |

| Fig. 2.8 : Common Collector Configuration                                       | 59 |

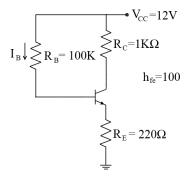

| Fig. 2.9 : Circuit under consideration                                          | 60 |

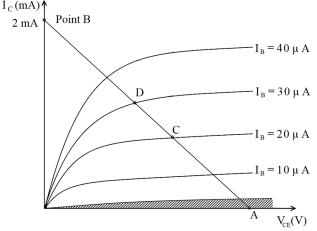

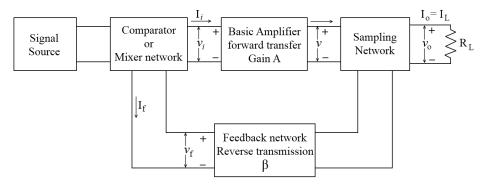

| Fig. 2.10 : DC Load Line                                                        | 60 |

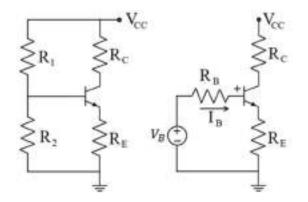

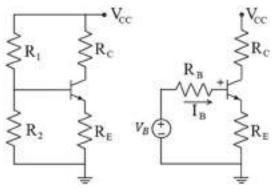

| Fig. 2.11 : Potential divider bias                                              | 62 |

| Fig. 2.12 : Self bias circuit                                                   | 64 |

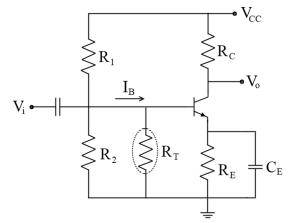

| Fig. 2.13 : Thermistor bias Compensation                                        | 64 |

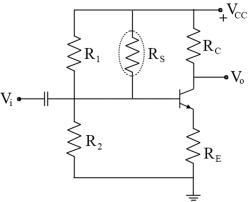

| Fig. 2.14 : Sensistor bias Compensation                                         | 65 |

| Fig. 2.15 : Transistor as Amplifier                                             | 65 |

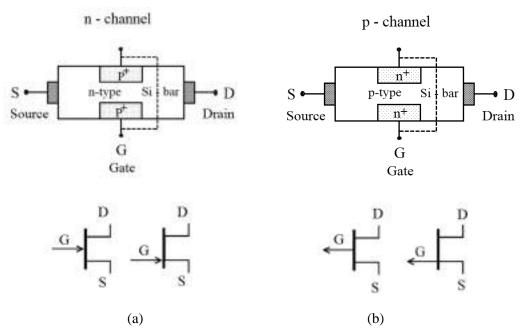

| Fig. 2.16 : Construction and symbol of an (a) n- channel and (b) p-channel JFET | 67 |

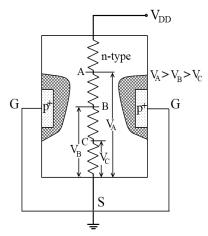

| Fig. 2.17 : N-Channel FET with applied drain voltage polarities                 | 67 |

| Fig. 2.18 : The rise in depletion width with applied $V_{DS}(V_{DD})$           | 68 |

| Fig. 2.19 : Depletion Region development due to internal voltage drop           | 68 |

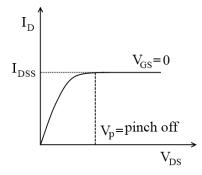

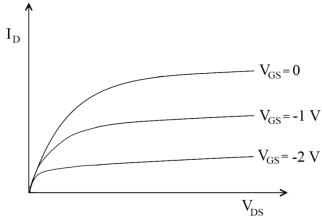

| Fig. 2.20 : Pinch-off occurs at $V_{GS} = V_P$                                  | 70 |

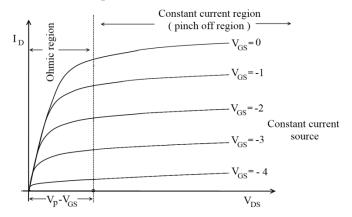

| Fig. 2.21 : Output Characteristics                                         | 70 |

|----------------------------------------------------------------------------|----|

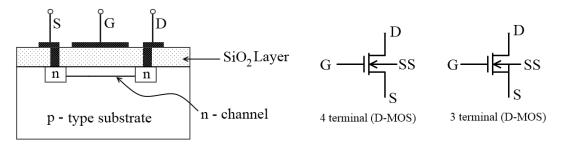

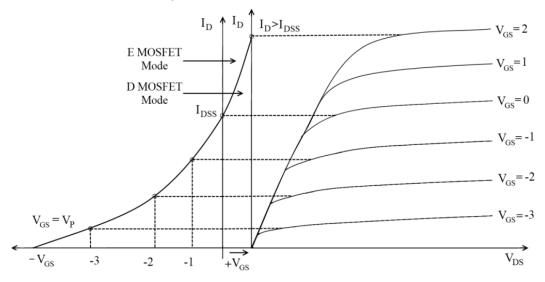

| Fig. 2.22 : Construction and symbol of a D-MOSFET                          | 72 |

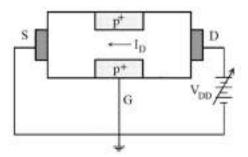

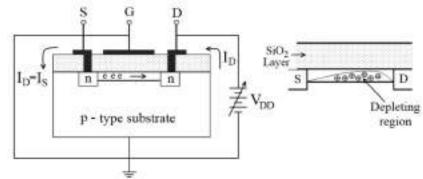

| Fig. 2.23 : Operation of a D-MOSFET at $V_{GS} = 0$                        | 72 |

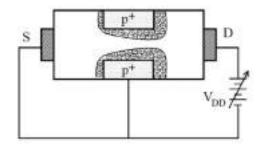

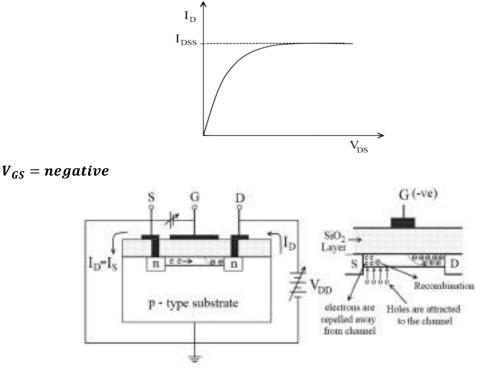

| Fig. 2.24 : Operation of a D-MOSFET at $V_{GS}$ =negative                  | 73 |

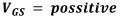

| Fig. 2.25 : Operation of a D-MOSFET at $V_{GS}$ =positive                  | 73 |

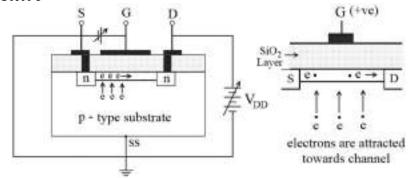

| Fig. 2.26 : The drain –source characteristics and transfer characteristics | 74 |

| Fig. 2.27 : Symbol of a p-channel D-MOSFET                                 | 75 |

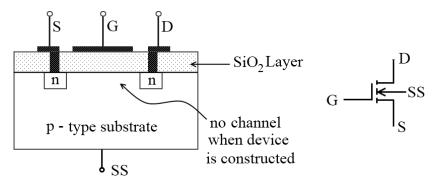

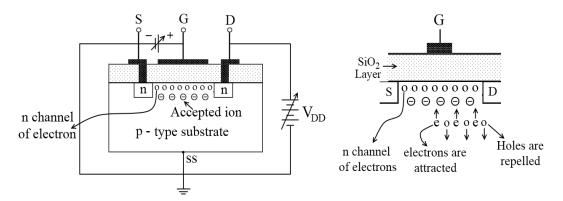

| Fig. 2.28 : Construction and symbol of an E-MOSFET                         | 75 |

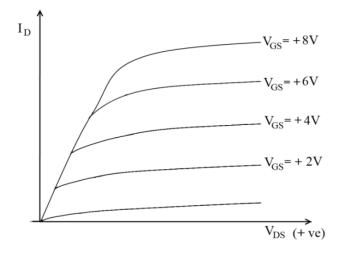

| Fig. 2.29 : Drain Source Characteristics                                   | 76 |

| Fig. 2.30 : Basic CMOS configuration                                       | 77 |

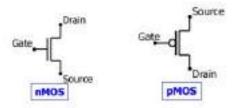

| Fig. 2.31 : Symbol of an NMOS and PMOS transistor                          | 77 |

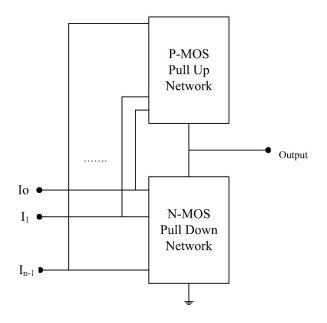

| Fig. 2.32 : CMOS using Pull up and Pull Down                               | 78 |

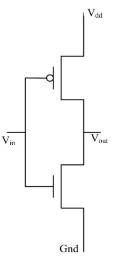

| Fig. 2.33 : CMOS Inverter                                                  | 79 |

## Unit 3 Feedback Amplifier and Oscillators

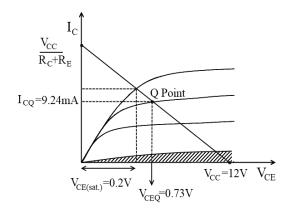

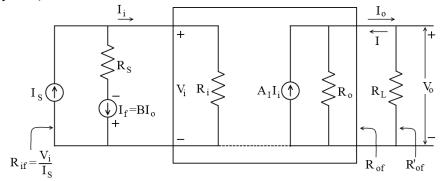

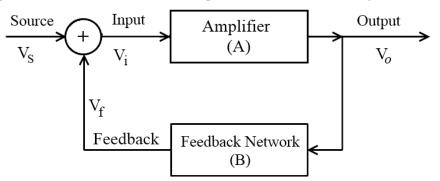

| Fig. 3.1 : A single-loop feedback system                                                | 91 |

|-----------------------------------------------------------------------------------------|----|

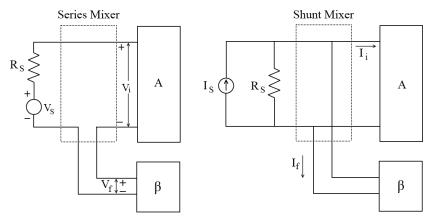

| Fig. 3.2 : Mixer Networks: (a) Voltage Comparator (b) Current Comparator                | 92 |

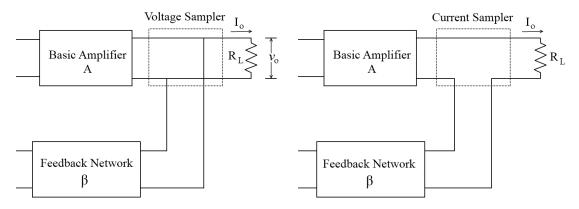

| Fig. 3.3 : Sampling Networks: (a) Voltage Sampling (b) Current Sampling                 | 92 |

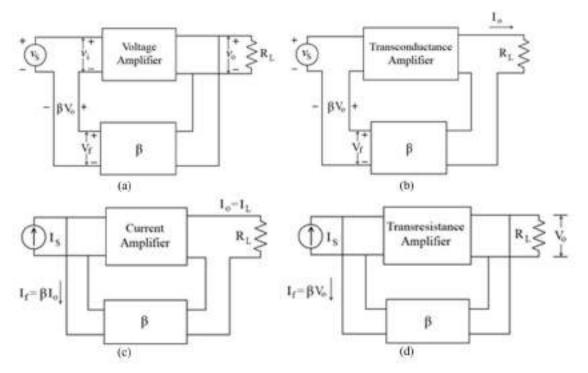

| Fig. 3.4 : Feedback amplifiers connection type: (a) Voltage series feedback (b) Current | 93 |

| series feedback (c) Current-shunt feedback d) Voltage-shunt feedback                    |    |

| Fig. 3.5 : Voltage series feedback connection                                           | 95 |

| Fig. 3.6 : Voltage-shunt feedback connection                                            | 95 |

| Fig. 3.7 : Current-Series feedback connection                                           | 97 |

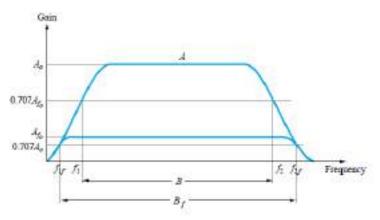

| Fig. 3.8 : Effect of negative feedback on gain and bandwidth                            | 98 |

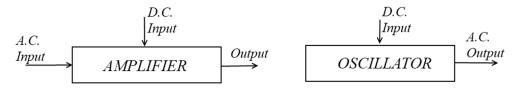

| Fig. 3.9 : Difference between amplifier and oscillator                                  | 99 |

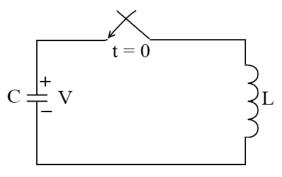

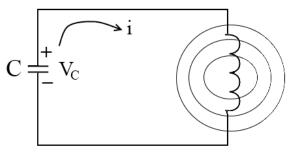

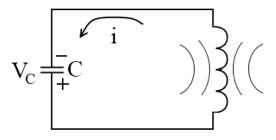

| Fig. 3.10 : Tank circuit ( LC-tuned circuit)                                            | 99 |

| Fig. 3.11 : Charging of an Inductor                      | 99  |

|----------------------------------------------------------|-----|

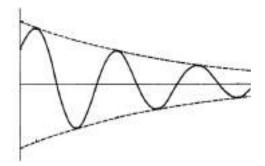

| Fig. 3.12 : Discharging of an Inductor                   | 100 |

| Fig. 3.13 : Damped Sinusoidal waveform                   | 100 |

| Fig. 3.14 : Block diagram of positive feedback amplifier | 101 |

| Fig. 3.15 : Oscillator classification chart              | 103 |

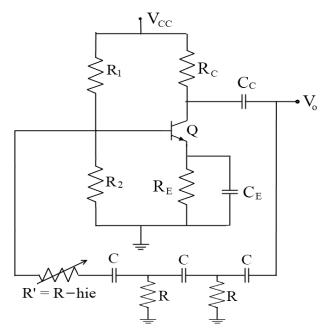

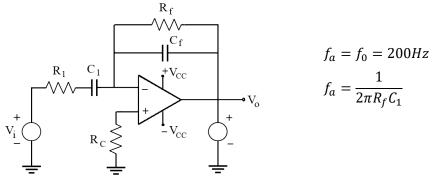

| Fig. 3.16 : RC phase shift oscillator                    | 104 |

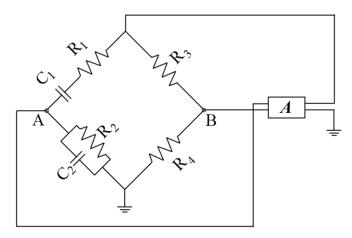

| Fig. 3.17 : A Wien Bridge Oscillator                     | 105 |

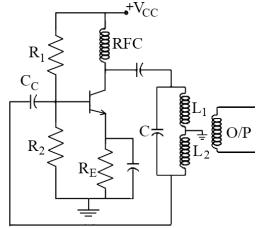

| Fig. 3.18 : Circuit diagram of Hartley oscillator        | 106 |

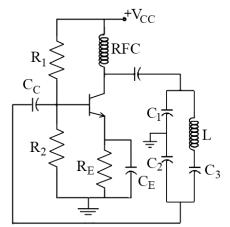

| Fig. 3.19 : Circuit diagram of Colpitts oscillator       | 107 |

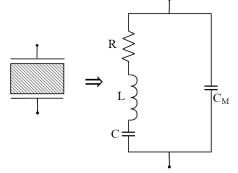

| Fig. 3.20 : Electrical equivalent circuit of crystal     | 108 |

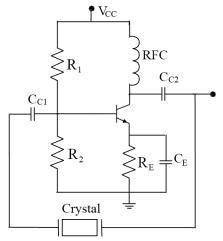

| Fig. 3.21 : Transistorized crystal oscillator            | 108 |

| Fig. 3.22 : Wien Bridge oscillator circuit               | 110 |

## Unit 4 Operational Amplifier and Application

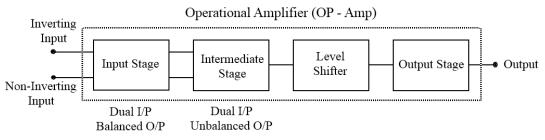

| Fig. 4.1 : Block diagram of Op-Amp                               | 116 |

|------------------------------------------------------------------|-----|

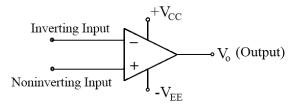

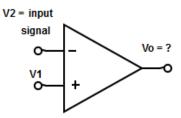

| Fig. 4.2 : Symbol of Op-Amp                                      | 117 |

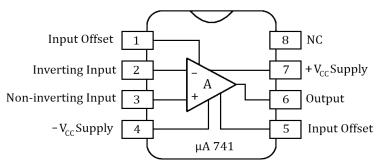

| Fig. 4.3 : Pin configuration of IC 741 Op-Amp                    | 117 |

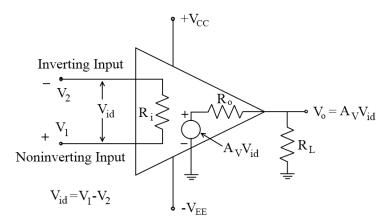

| Fig. 4.4 : Op-Amp equivalent circuit                             | 118 |

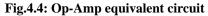

| Fig. 4.5 : Op-Amp equivalent circuit for an ideal case           | 118 |

| Fig. 4.6 : Circuit arrangement for calculation of offset voltage | 119 |

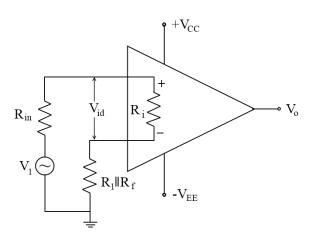

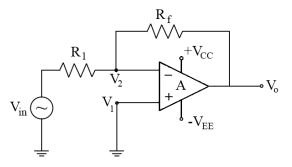

| Fig. 4.7 : Op-Amp inverting amplifier                            | 120 |

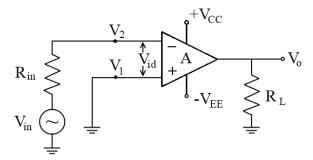

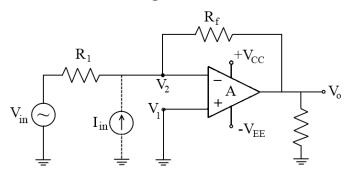

| Fig. 4.8 : Open loop inverting amplifier                         | 121 |

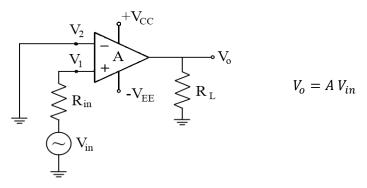

| Fig. 4.9 : Open-loop non-inverting amplifier                     | 122 |

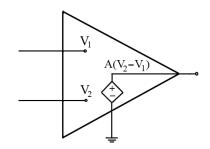

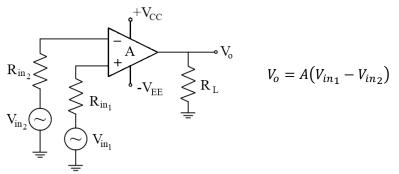

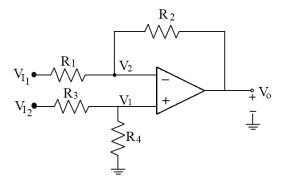

| Fig. 4.10 : Differential amplifier using OP-Amp                  | 122 |

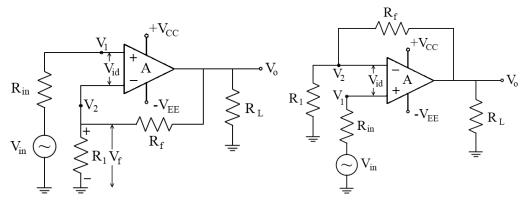

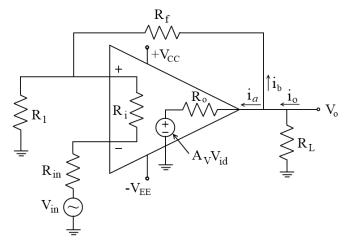

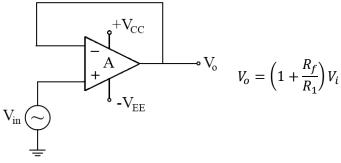

| Fig. 4.11 : Non-Inverting Amplifier with Feedback                | 123 |

| Fig. 4.12 : Equivalent circuit for input impedance calculation   | 124 |

| Fig. 4.13 : Equivalent circuit for output impedance calculation   | 125 |

|-------------------------------------------------------------------|-----|

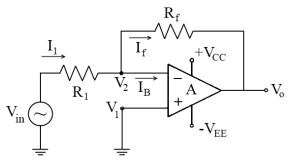

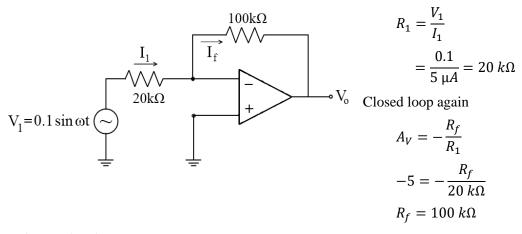

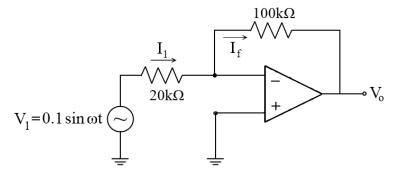

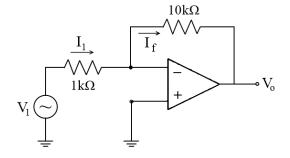

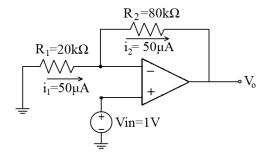

| Fig. 4.14 : Inverting Amplifier with feedback                     | 126 |

| Fig. 4.15 : Voltage follower circuit                              | 126 |

| Fig. 4.16 : Op-Amp as an Inverter                                 | 127 |

| Fig. 4.17 : Op-Amp as Current to voltage converter                | 127 |

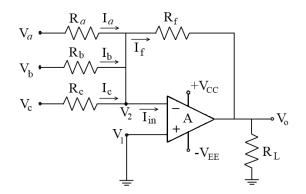

| Fig. 4.18 : Inverting summing amplifier                           | 128 |

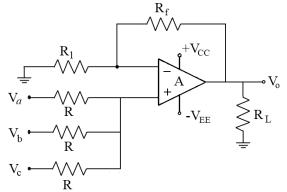

| Fig. 4.19 : Non-inverting summing amplifier                       | 129 |

| Fig. 4.20 : Op-Amp as a Subtractor                                | 131 |

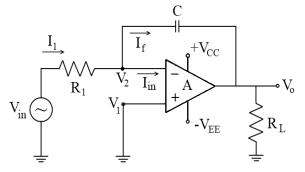

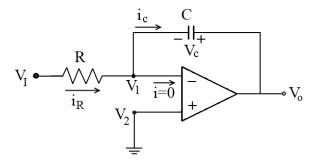

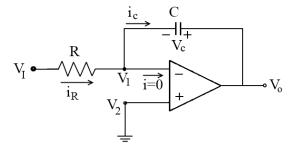

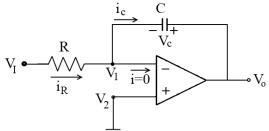

| Fig. 4.21 : Op-Amp Integrator circuit                             | 132 |

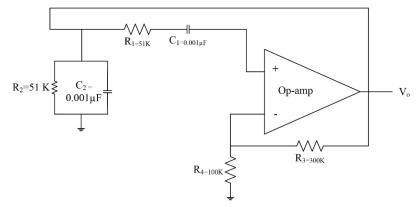

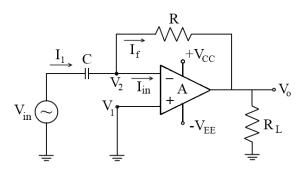

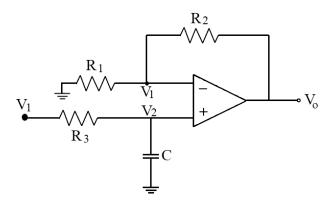

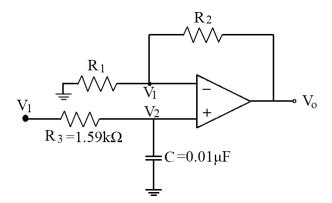

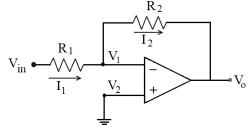

| Fig. 4.22 : Op-Amp differentiator circuit                         | 133 |

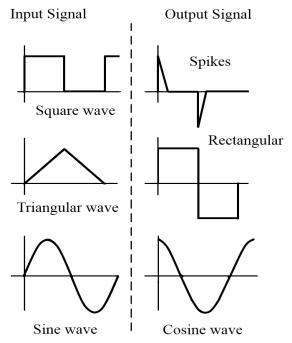

| Fig. 4.23 : Input and Output waveform of a Differentiator         | 133 |

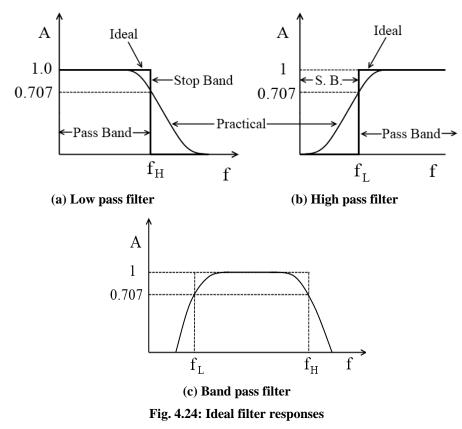

| Fig. 4.24 : Ideal filter response                                 | 134 |

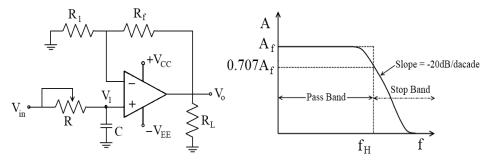

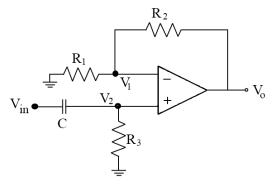

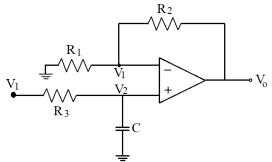

| Fig. 4.25 : (a) A first-order low pass filter (b) Filter response | 134 |

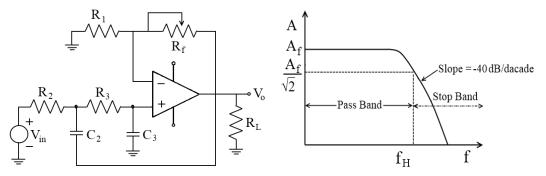

| Fig. 4.26 : (a) Second order Low pass filter (b) Filter response  | 135 |

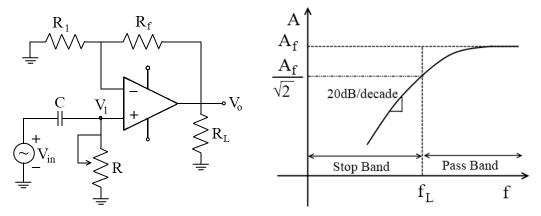

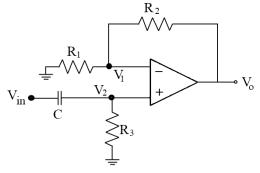

| Fig. 4.27 : (a) First order High pass filter (b) Filter response  | 135 |

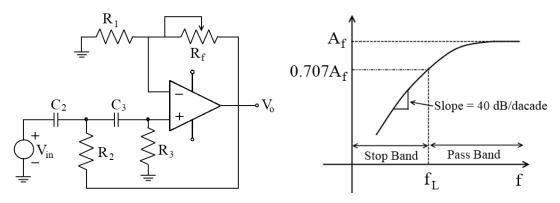

| Fig. 4.28 : (a) Second order High pass filter (b) Filter response | 136 |

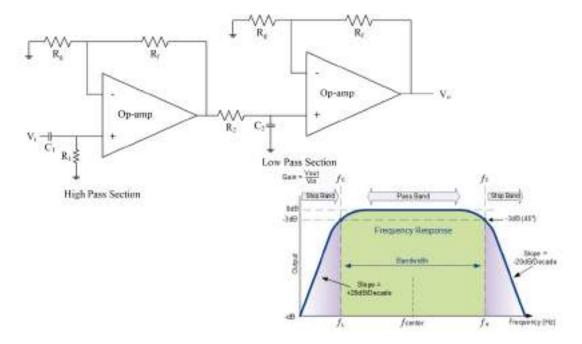

| Fig. 4.29 : A bandpass active filter                              | 136 |

## Unit 5 Measuring Instruments & Transducers

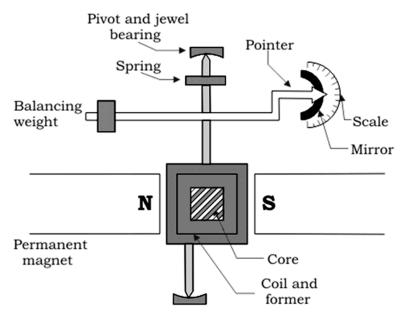

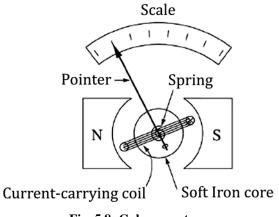

| Fig. 5.1 : Construction of D' Arsonval Instrument                | 159 |

|------------------------------------------------------------------|-----|

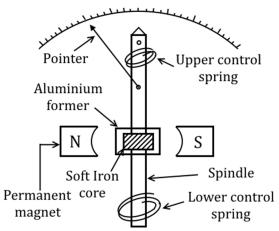

| Fig. 5.2 : Instrument for Permanent Magnet Moving Coil (PMMC)    | 160 |

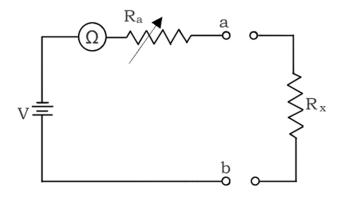

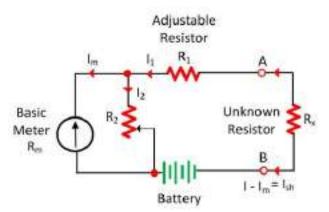

| Fig. 5.3 : Ohmmeter                                              | 162 |

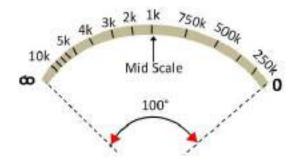

| Fig. 5.4 : A series ohmmeter                                     | 163 |

| Fig. 5.5 : Scale of a series ohmmeter                            | 163 |

| Fig. 5.6 : (a) Shunt type ohmmeter (b) Scale of a shunt ohmmeter | 164 |

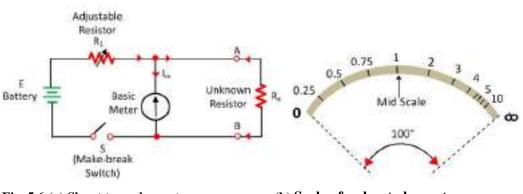

| Fig. 5.7 : Multirange Ohmmeter                                   | 165 |

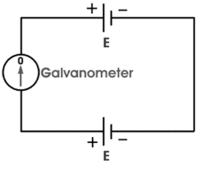

| Fig. 5.8 : Galvanometer                                       | 165 |

|---------------------------------------------------------------|-----|

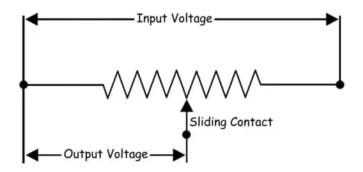

| Fig. 5.9 : Concept of a potentiometer                         | 167 |

| Fig. 5.10 : Potentiometer                                     | 168 |

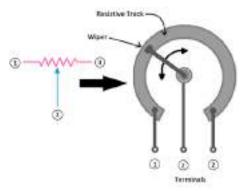

| Fig. 5.11 : A rotary potentiometer                            | 168 |

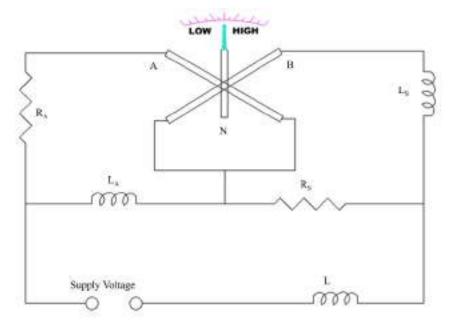

| Fig. 5.12 : Construction of a moving iron frequency meter     | 169 |

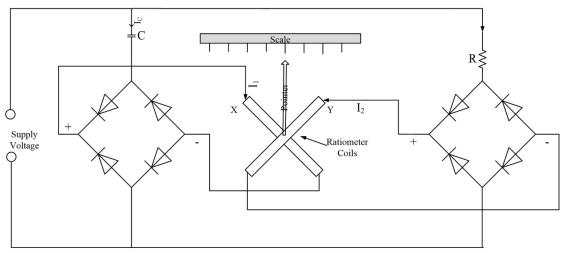

| Fig. 5.13 : Construction of an Electrodynamic frequency meter | 170 |

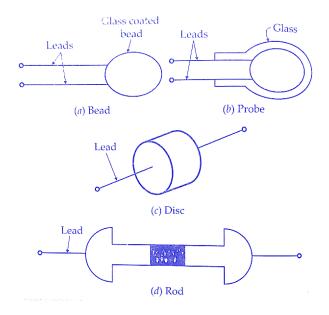

| Fig. 5.14 : Types of Thermistors                              | 179 |

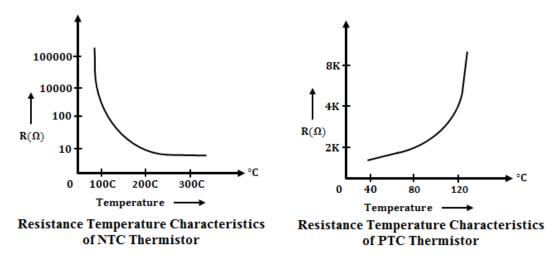

| Fig. 5.15 : Resistance-Temperature characteristics            | 179 |

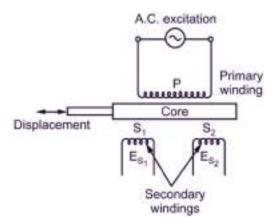

| Fig. 5.16 :The construction of LVDT                           | 181 |

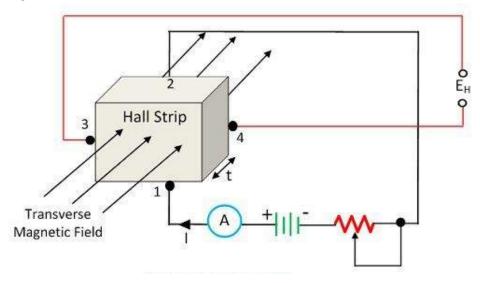

| Fig. 5.17 : Hall Effect element                               | 184 |

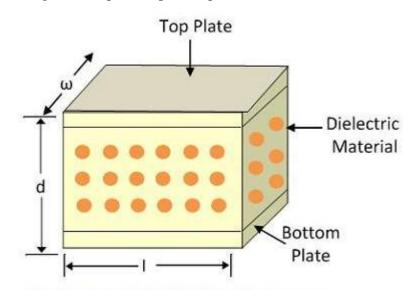

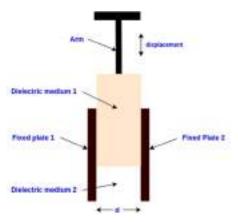

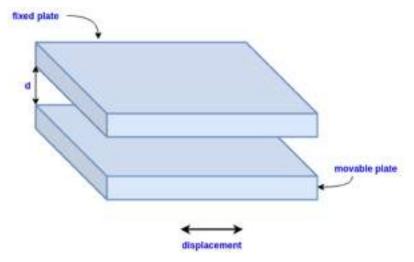

| Fig. 5.18 : Parallel plate capacitive transducer              | 186 |

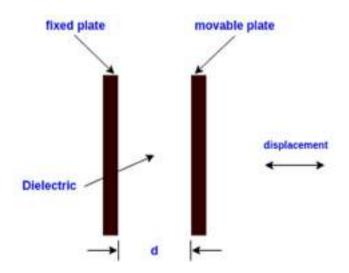

| Fig. 5.19 : Variation in the distance between two plates      | 187 |

| Fig. 5.20 : Capacitance between two plates                    | 188 |

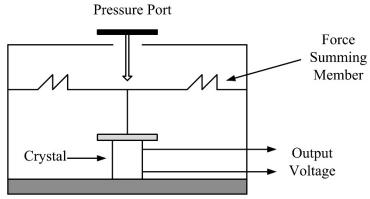

| Fig. 5.21 : Piezoelectric transducer                          | 190 |

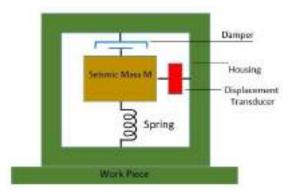

| Fig. 5.22 : Construction of a seismic transducer              | 192 |

## Unit 6 Introduction to Digital Electronics

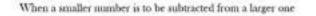

| Fig. 6.1 : Illustration of 9's complement arithmetic   | 206 |

|--------------------------------------------------------|-----|

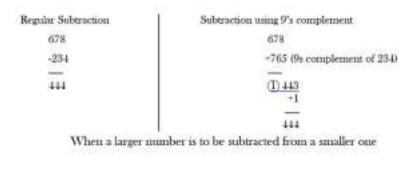

| Fig. 6.2 : Illustration of 10's complement arithmetic  | 207 |

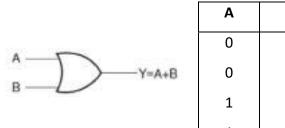

| Fig. 6.3 : A Two-input OR gate and its truth table     | 233 |

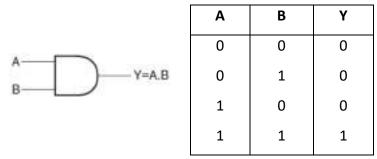

| Fig. 6.4 : A Two-input AND gate and its truth table    | 234 |

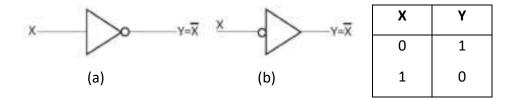

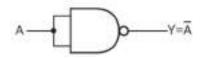

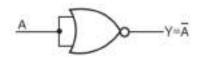

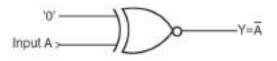

| Fig. 6.5 : Symbol of a NOT gate and its truth table    | 234 |

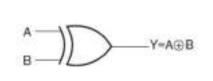

| Fig. 6.6 : A Two-input Ex-OR gate                      | 235 |

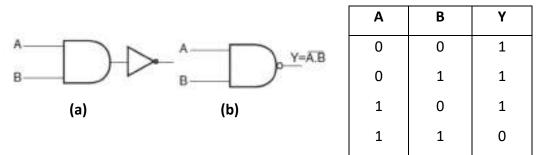

| Fig. 6.7 : A Two-input NAND gate and its truth table   | 235 |

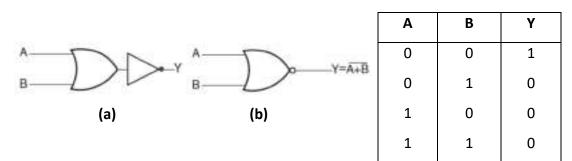

| Fig. 6.8 : A Two-input NOR gate and its truth table    | 236 |

| Fig. 6.9 : A Two-input Ex-NOR gate and its truth table | 236 |

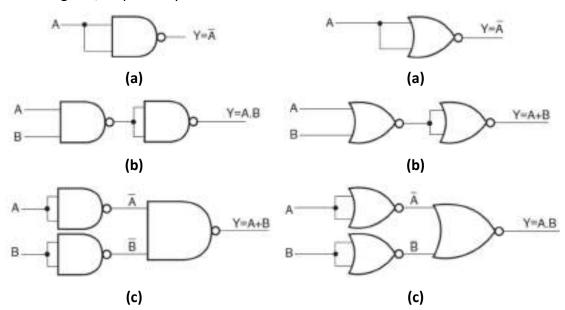

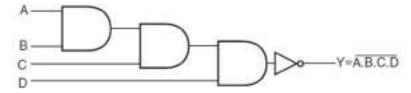

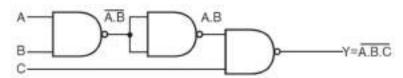

| Fig. 6.10 : NAND gate as a Universal gate       | 237 |

|-------------------------------------------------|-----|

| Fig. 6.11 : NOR gate as a Universal gate        | 237 |

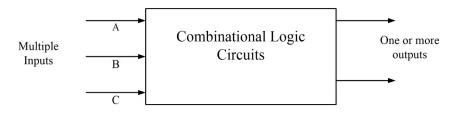

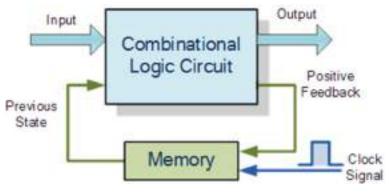

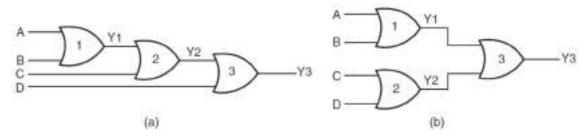

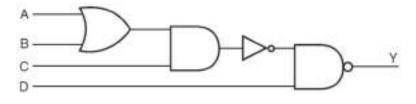

| Fig. 6.12 : A combinational logic               | 240 |

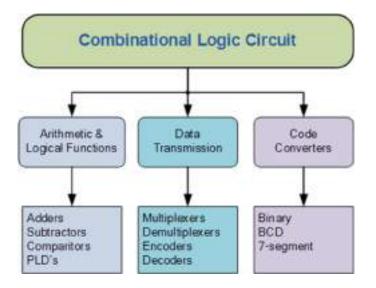

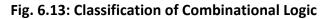

| Fig. 6.13 : Classification of Combination Logic | 241 |

| Fig. 6.14 : Sequential logic                    | 242 |

## LIST OF TABLES

| Unit 1 Diode and Its Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table. 1.1 : Comparison of Zener and Avalanche Breakdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34  |

| Unit 3 Feedback Amplifier and Oscillators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| Table. 3.1 : Summary of Gain, Feedback, and Gain with feedback from Fig.3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 94  |

| Table. 3.2 : Summarizes the effect of feedback on input and output impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 97  |

| Unit 5 Measuring Instruments & Transducers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| Table. 5.1 :Key difference between a sensor and a transducer       Item (Second Second S | 172 |

| Table. 5.2 : Gauge Factor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 177 |

| Unit 6 Introduction to Digital Electronics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| Table. 6.1 : Octal to Binary Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 215 |

| Table. 6.2 : Hexadecimal to Binary Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 222 |

| Table. 6.3 : BCD code representations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 224 |

| Table. 6.4 : Excess-3 code for the decimal numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 226 |

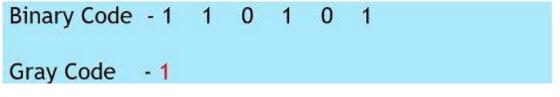

| Table. 6.5 : Gray code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 227 |

| Table. 6.6 : Comparison between the Combinational and Sequential Logic Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 243 |

## CONTENTS

| Foreword                  | iv   |

|---------------------------|------|

| Acknowledgment            | v    |

| Preface                   | vi   |

| Outcome Based Education   | vii  |

| Course Outcomes           | viii |

| Guidelines for Teachers   | ix   |

| Guidelines for Students   | x    |

| Abbreviations and Symbols | x    |

| List of Figures           | xii  |

| List of Tables            | xx   |

|                           |      |

| Un         | it 1: Diode and Its Applications                               | 1-50          |

|------------|----------------------------------------------------------------|---------------|

|            | Rationale                                                      | 1             |

|            | Unit Outcomes                                                  | 1             |

|            | Learning Objective                                             | 1             |

|            | Mapping the unit outcome with course outcomes                  | 2             |

| 1.1        | Review of a P-N junction                                       | 3             |

| 1.2        | The V-I Characteristics                                        | 3             |

| 1.3        | Semiconductor band and Fermi energy levels                     | 5             |

|            | 1.3.1 Position of Fermi level in doped Semiconductors          | 5             |

|            | 1.3.2 Energy Band Diagram for a P-N junction                   | 5             |

|            | 1.3.3 Built-in voltage of the P-N junction                     | 6             |

| 1.4        | P-N Junction with external bias                                | 7             |

|            | 1.4.1 Zero bias voltage                                        | 7             |

|            | 1.4.2 Forward bias condition                                   | 8             |

|            | 1.4.3 Energy band diagrams for P-N junction with external bias | 11            |

| 1.5        | Static and dynamic resistance of a P-N junction diode          | 11            |

| 1.6        | Diode capacitance                                              | 12            |

| 1.7        | Temperature Effect on Diode                                    | 14            |

| 1.8        | Switching time of a Diode                                      | 15            |

| 1.9        | DC Power Supply                                                | 16            |

|            | Solved Examples                                                | 43            |

|            | Exercises Questions                                            | 45            |

|            | Self-Study Questions                                           | 45            |

|            | Multiple Choice Questions                                      | 46            |

|            | Attainment & Gap Analysis                                      | 50            |

| <b>T</b> 7 | it ). Transiston Changeteristics                               | <b>51</b> .00 |

| Unit 2. Transision Characteristics | 51-00 |

|------------------------------------|-------|

| Rationale                          | 50    |

| Unit Outcomes                      | 50    |

|                                    |       |

|      | Learning Objective                                           | 50     |

|------|--------------------------------------------------------------|--------|

|      | Mapping the unit outcome with the course outcomes            | 50     |

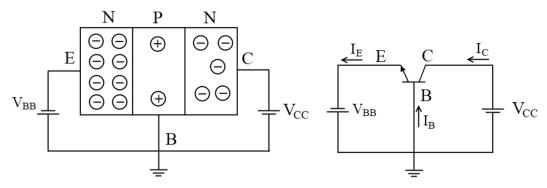

| 2.1  | Bipolar Junction Transistor (BJT)                            | 53     |

| 2.2  | Modes (Regions) of operation of BJT                          | 54     |

| 2.3  | Transistor operation in linear mode                          | 55     |

|      | 2.3.1 For NPN transistor                                     | 55     |

|      | 2.3.2 For PNP transistor                                     | 56     |

| 2.4  | Transistor Configuration                                     | 57     |

|      | 2.4.1 Common Base Configuration (CB)                         | 57     |

|      | 2.4.2 Common Emitter Configuration(CE)                       | 58     |

|      | 2.4.2 Common Collector Configuration(CC)                     | 59     |

| 2.5  | DC Load Line                                                 | 59     |

| 2.6  | Transistor biasing                                           | 61     |

| 2.7  | Thermal Stability                                            | 63     |

|      | 2.7.1 Generalized Expression for S                           | 63     |

|      | 2.7.2 Bias Compensation                                      | 64     |

| 2.8  | Transistor as Amplifier                                      | 65     |

| 2.9  | The Field Effect Transistor (FET)                            | 66     |

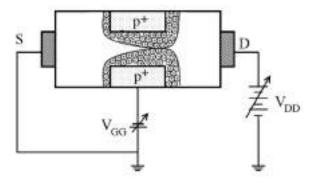

|      | 2.9.1 Junction Field effect transistors (JFET)               | 66     |

|      | 2.9.2 Operation of a JFET (n-channel)                        | 67     |

|      | 2.9.3 FET Parameters                                         | 70     |

|      | 2.9.4 Comparison between BJT and FET                         | 71     |

| 2.10 | ) MOSFET (Metal oxide semiconductor field effect transistor) | 71     |

|      | 2.10.1 D-MOSFET (n-channel)                                  | 72     |

|      | 2.10.2 E-MOSFET (n-channel)                                  | 75     |

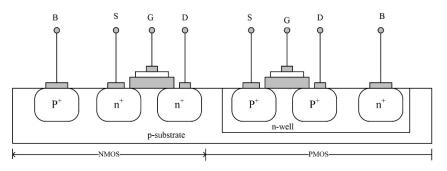

| 2.11 | CMOS                                                         | 77     |

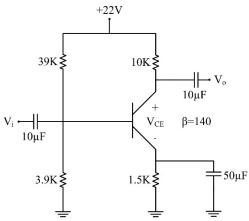

|      | Solved Example                                               | 80     |

|      | Exercises Questions                                          | 83     |

|      | Self-Study Questions                                         | 84     |

|      | Multiple Choice Questions                                    | 84     |

|      | Attainment & Gap Analysis                                    | 88     |

| Uni  | it 3: Feedback Amplifier and Oscillators                     | 89-113 |

|      | Rationale                                                    | 89     |

|      | Unit Outcomes                                                | 89     |

|      | Learning Objective                                           | 89     |

|      | Mapping the unit outcome with the course outcomes            | 89     |

| 3.1  | The concept of feedback                                      | 91     |

| 3.2  | Feedback connection types                                    | 93     |

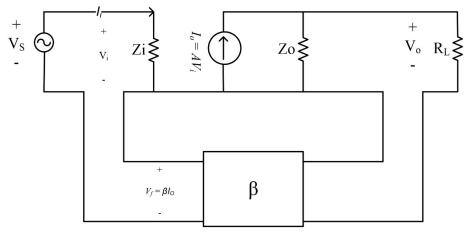

| 3.3  | The gain with feedback                                       | 94     |

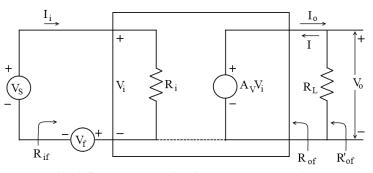

| 3.4  | Input Impedance with feedback                                | 95     |

| 3.5  | Output Impedance with feedback                               | 96     |

| 3.6  | General characteristics of a negative feedback amplifier     | 97     |

| 3.7  | Oscillators                                                  | 99     |

| 3.8  | Block Diagram of Positive Feedback Amplifier                 | 101    |

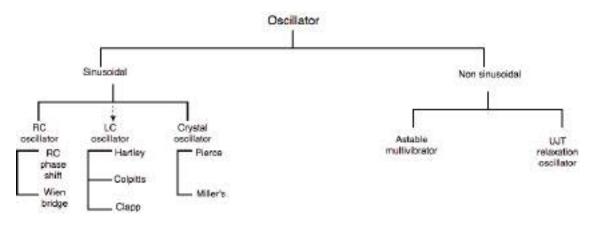

| 3.9  | Classification of Oscillator                                 | 102    |

| 3.10 RC phase shift oscillator | 103 |

|--------------------------------|-----|

| 3.11 Wien Bridge Oscillator    | 105 |

| 3.12 LC Oscillator             | 106 |

| 3.12.1 Hartley Oscillator      | 106 |

| 3.12.2 Colpitts Oscillator     | 107 |

| 3.12.3 Crystal Oscillator      | 107 |

| Solved Example                 | 109 |

| Exercises Questions            | 110 |

| Self-Study Questions           | 110 |

| Multiple Choice Questions      | 111 |

| Attainment & Gap Analysis      | 113 |

|                                |     |

## Unit 4: Operational Amplifier and Applications

114-155