M.Sc. (IT) Final Year

**MIT-11**

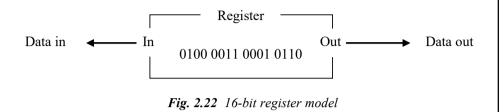

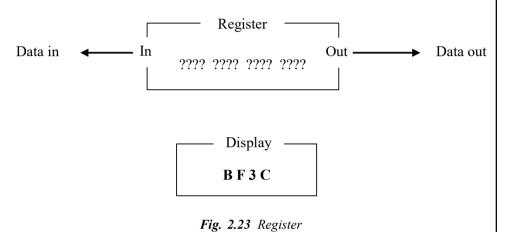

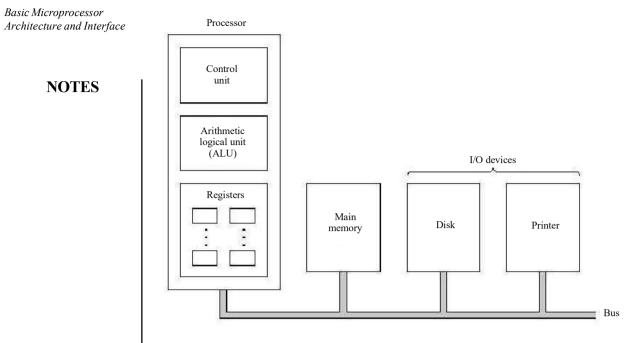

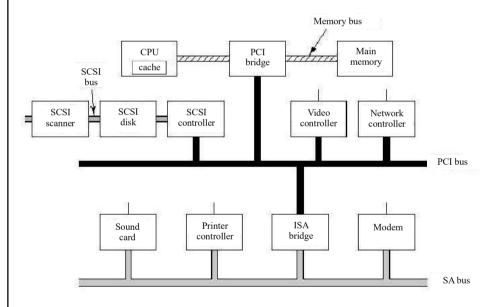

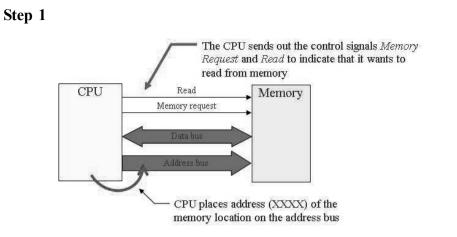

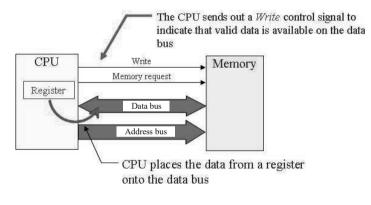

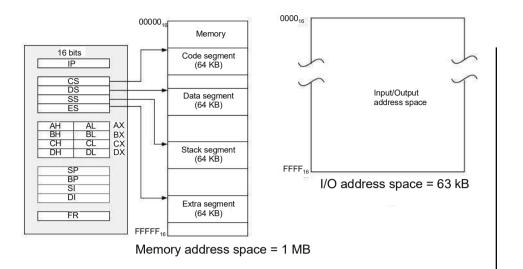

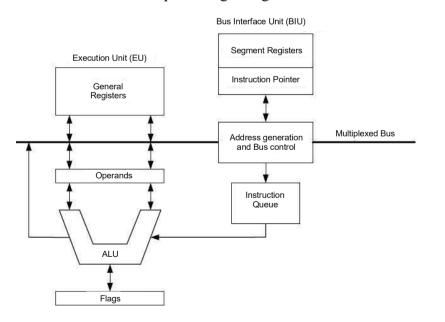

# MICROPROCESSOR AND ASSEMBLY LANGUAGE PROGRAMMING

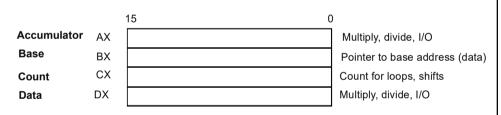

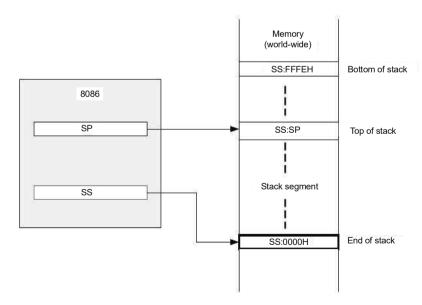

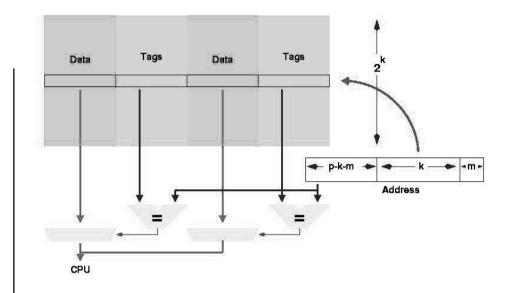

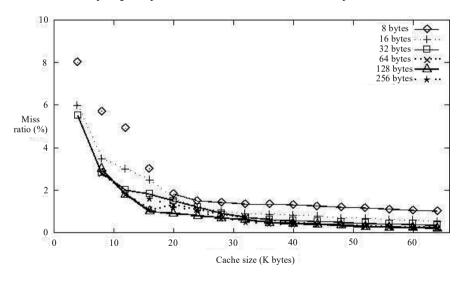

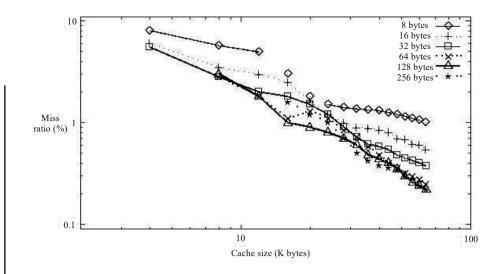

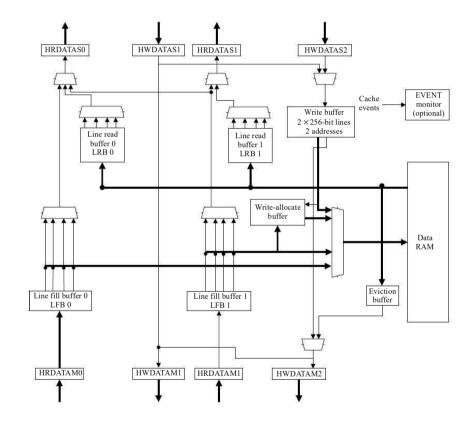

मध्यप्रदेश भोज (मुक्त) विश्वविद्यालय – भोपाल MADHYA PRADESH BHOJ (OPEN) UNIVERSITY - BHOPAL

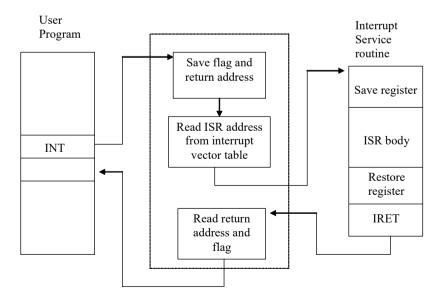

#### **Reviewer Committee**

- 1. Dr. Pragyesh Agrawal Director Institute for Excellence in Higher Education, Bhopal (M.P.)

- 2. Dr. Romsha Sharma Professor Sri Sathya Sai College for Women, Bhopal (M.P.)

#### Advisory Committee

**COURSEWRITER**

Units (1-5)

- 1. Dr. Jayant Sonwalkar Hon'ble Vice Chancellor Madhya Pradesh Bhoj (Open) University, Bhopal (M.P.)

- 2. Dr. L.S. Solanki Registrar Madhya Pradesh Bhoj (Open) University, Bhopal (M.P.)

- 3. Dr. Kishor John Director Madhya Pradesh Bhoj (Open) University, Bhopal (M.P.)

3. Dr. Sharad Gangale Professor *R.K.D.F. University, Bhopal (M.P.)*

- 4. Dr. Pragyesh Agrawal Director Institute for Excellence in Higher Education, Bhopal (M.P.)

- 5. Dr. Romsha Sharma Professor Sri Sathya Sai College for Women, Bhopal (M.P.)

- 6. Dr. Sharad Gangale Professor *R.K.D.F. University, Bhopal (M.P.)*

Copyright © Reserved, Madhya Pradesh Bhoj (Open) University, Bhopal

All rights reserved. No part of this publication which is material protected by this copyright notice may be reproduced or transmitted or utilized or stored in any form or by any means now known or hereinafter invented, electronic, digital or mechanical, including photocopying, scanning, recording or by any information storage or retrieval system, without prior written permission from the Registrar, Madhya Pradesh Bhoj (Open) University, Bhopal

Vikas Kumar, Assistant Professor (IT), Asia Pacific Institute of Management, New Delhi

Information contained in this book has been published by VIKAS<sup>®</sup> Publishing House Pvt. Ltd. and has been obtained by its Authors from sources believed to be reliable and are correct to the best of their knowledge. However, the Madhya Pradesh Bhoj (Open) University, Bhopal, Publisher and its Authors shall in no event be liable for any errors, omissions or damages arising out of use of this information and specifically disclaim any implied warranties or merchantability or fitness for any particular use.

Published by Registrar, MP Bhoj (open) University, Bhopal in 2020

Vikas<sup>®</sup> is the registered trademark of Vikas<sup>®</sup> Publishing House Pvt. Ltd.

VIKAS® PUBLISHING HOUSE PVT. LTD.

E-28, Sector-8, Noida - 201301 (UP)

Phone: 0120-4078900 • Fax: 0120-4078999

Regd. Office: A-27, 2nd Floor, Mohan Co-operative Industrial Estate, New Delhi 1100 44

Website: www.vikaspublishing.com • Email: helpline@vikaspublishing.com

# SYLLABI-BOOK MAPPING TABLE

# Microprocessor and Assembly Language Programming

| Syllabi                                                                                                                                                                                                                                             | Mapping in Book                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| UNIT - I<br>Introduction to Microprocessor: Evolution of Microprocessor, Overview<br>of Intel Pro-Pentium, Motorola 68000 Series, Introduction to DEC Alpha,<br>PowerPC, RISC & CISC Architecture.                                                  | Unit-1: Introduction to<br>Microprocessor<br>(Pages 3-31)                   |

| UNIT - II<br>Basic Microprocessor Architecture and Interface: Internal Architecture,<br>External System, Bus Architecture, Memory and Input/Output Interface.                                                                                       | Unit-2: Basic Microprocessor<br>Architecture and Interface<br>(Pages 33-88) |

| <b>UNIT - III</b><br><b>Programming Mode:</b> Register Organization of 8086, Memory Addressing<br>and Instruction Formats, Memory Interfacing, Cache Memory and Cache<br>Controllers.                                                               | Unit-3: Programming Mode<br>(Pages 89-142)                                  |

| <b>UNIT - IV</b><br><b>Basic I/O Interface:</b> I/O Interface, 8255 Programmable Interface, 8254<br>Programmable Timer, 8251 Programmable/Communication Interface,<br>Interrupts, 8259 Programmable Interrupts Controller.                          | Unit-4: Basic I/O Interface<br>(Pages 143-175)                              |

| UNIT - V<br>8086 Assembly Language Programming: Instruction Set of 8086,<br>Assembler Directives and Operators, A Few Machine Level Programs,<br>Machine Coding and Programs, Programming with an Assembler, Assembly<br>Language Example Programs. | Unit-5: 8086 Assembly Language<br>Programming<br>(Pages 177-212)            |

# **CONTENTS**

#### **INTRODUCTION**

#### UNIT 1 INTRODUCTION TO MICROPROCESSOR

- 1.0 Introduction

- 1.1 Objectives

- 1.2 Introduction to Microprocessor

- 1.2.1 Evolution of Microprocessors

- 1.2.2 Performance of a Microprocessor

- 1.3 Overview of Intel Pro-Pentium

- 1.4 Motorola 68000 Series

- 1.5 Introduction to DEC Alpha

- 1.6 PowerPC

- 1.7 RISC & CISC Architecture

- 1.8 Answers to 'Check Your Progress'

- 1.9 Summary

- 1.10 Key Terms

- 1.11 Self-Assessment Questions and Exercises

- 1.12 Further Reading

#### UNIT 2 BASIC MICROPROCESSOR ARCHITECTURE AND INTERFACE 33-88

- 2.0 Introduction

- 2.1 Objectives

- 2.2 Internal Architecture of Microprocessor

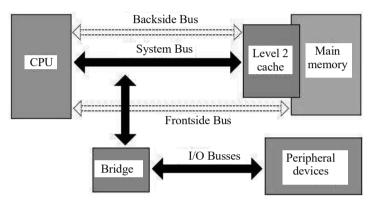

- 2.3 External System and Bus Architecture 2.3.1 The System Bus

- 2.4 Memory

- 2.5 Input/Output (I/O) Interface

- 2.6 Answers to 'Check Your Progress'

- 2.7 Summary

- 2.8 Key Terms

- 2.9 Self-Assessment Questions and Exercises

- 2.10 Further Reading

#### UNIT 3 PROGRAMMING MODE

- 3.0 Introduction

- 3.1 Objectives

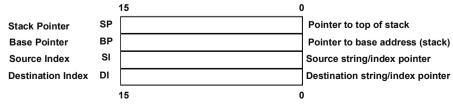

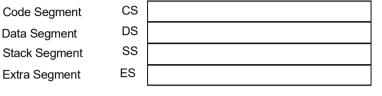

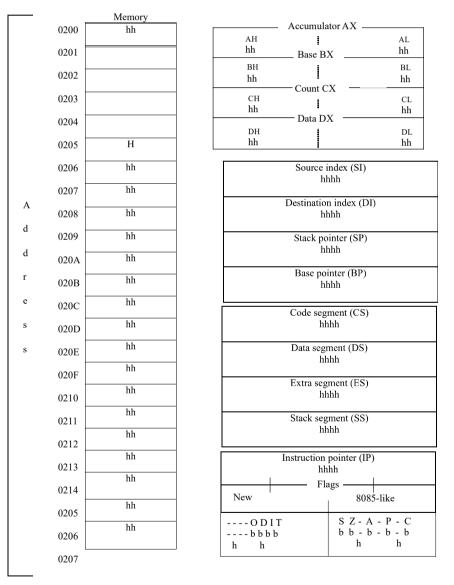

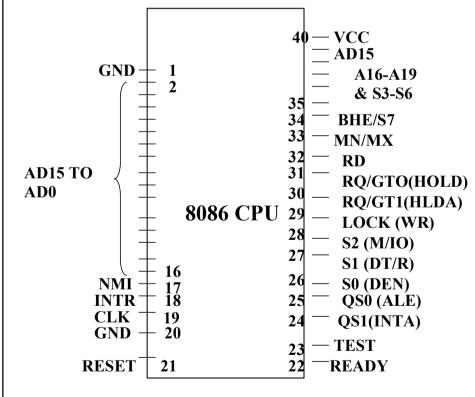

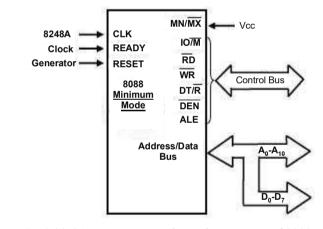

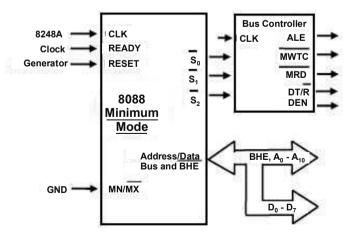

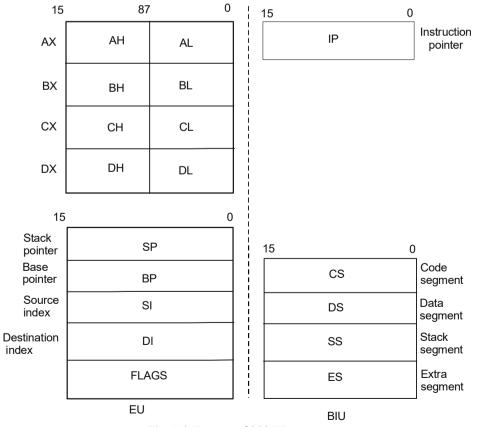

- 3.2 Register Organization of 8086 3.2.1 The Architecture of 8086

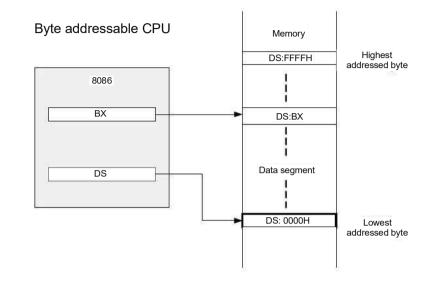

- 3.3 Memory Addressing

- 3.4 Instruction Formats

- 3.5 Cache Memory and Cache Controllers

- 3.6 Memory Interfacing

- 3.7 Answers to 'Check Your Progress'

- 3.8 Summary

- 3.9 Key Terms

- 3.10 Self-Assessment Questions and Exercises

- 3.11 Further Reading

89-142

3-31

#### UNIT 4 BASIC I/O INTERFACE

- 4.0 Introduction

- 4.1 Objectives

- 4.2 I/O Interface

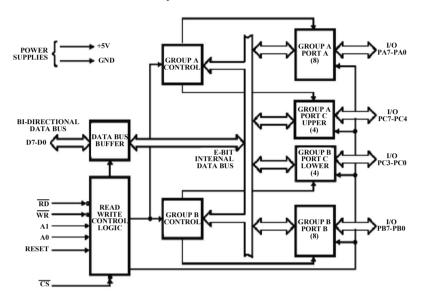

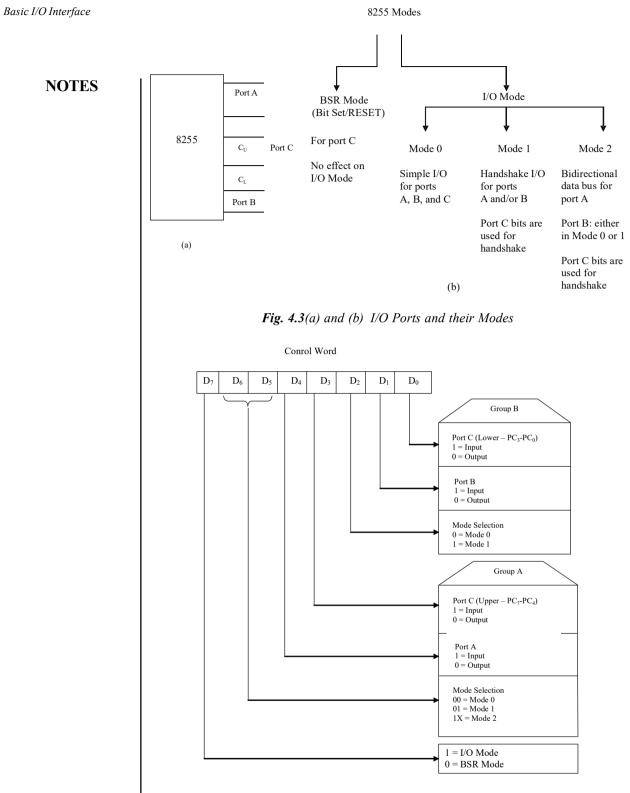

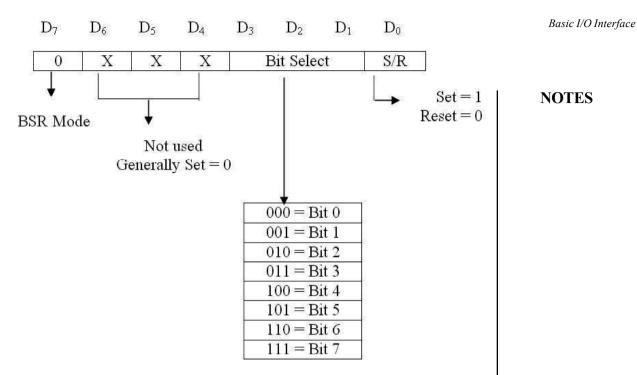

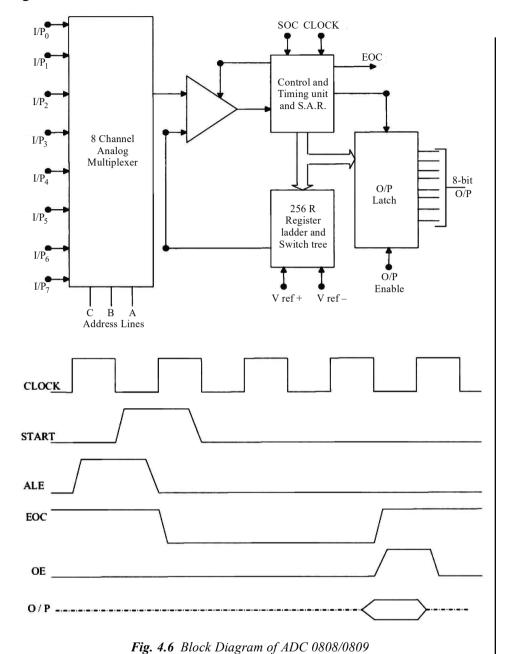

- 4.3 8255 Programmable Interface

- 4.4 8254 Programmable Timer

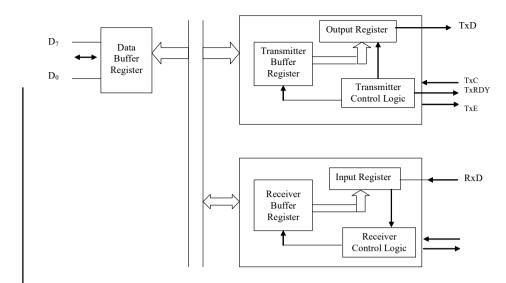

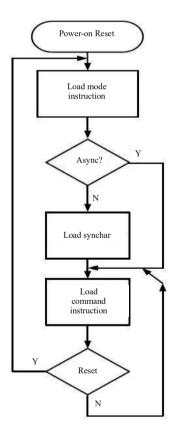

- 4.5 8251 Programmable/Communication Interface

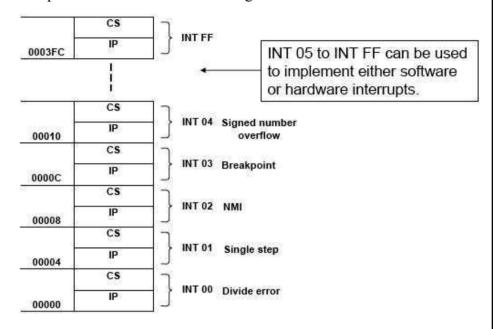

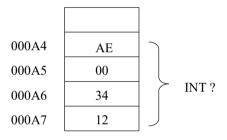

- 4.6 Interrupts

- 4.7 8259 Programmable Interrupts Controller

- 4.8 Answers to 'Check Your Progress'

- 4.9 Summary

- 4.10 Key Terms

- 4.11 Self-Assessment Questions and Exercises

- 4.12 Further Reading

#### UNIT 5 8086 ASSEMBLY LANGUAGE PROGRAMMING

177-212

- 5.0 Introduction

- 5.1 Objectives

- 5.2 Instruction Set of 8086

- 5.3 Assembler Directives and Operators

- 5.4 Machine Coding and Programs

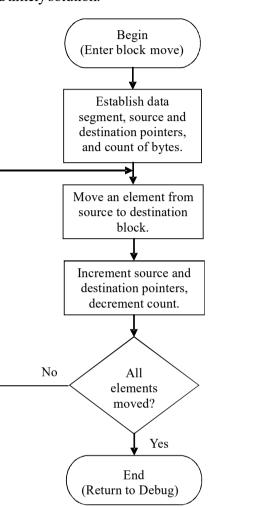

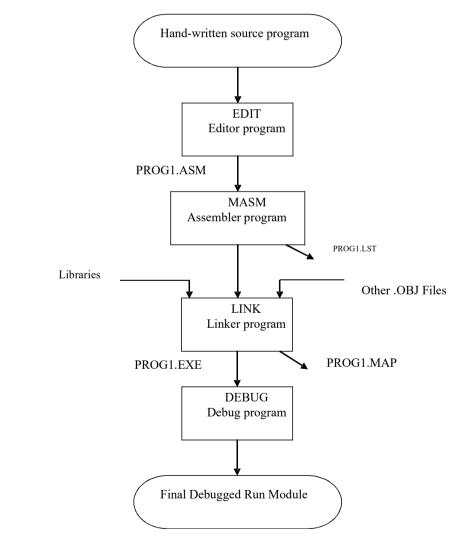

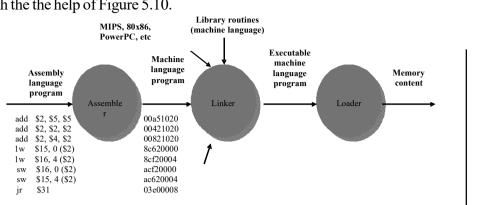

- 5.5 Programming with an Assembler

- 5.6 Assembly Language Example Programs

- 5.7 Answers to 'Check Your Progress'

- 5.8 Summary

- 5.9 Key Terms

- 5.10 Self-Assessment Questions and Exercises

- 5.11 Further Reading

Introduction

### **INTRODUCTION**

A microprocessor is a computer processor where the data processing logic and control is included on a single integrated circuit, or a small number of integrated circuits. The microprocessor contains the arithmetic, logic, and control circuitry required to perform the functions of a computer's Central Processing Unit (CPU). The integrated circuit is capable of interpreting and executing program instructions and performing arithmetic operations. The microprocessor is a multipurpose, clock-driven, register-based, digital integrated circuit that accepts binary data as input, processes it according to instructions stored in its memory, and provides results (also in binary form) as output. Microprocessors contain both combinational logic and sequential digital logic, and operate on numbers and symbols represented in the binary number system. The integrated circuit processors are produced the cost of processing power. Integrated circuit processors are produced in large numbers by highly automated Metal-Oxide-Semiconductor (MOS) fabrication processes, resulting in a relatively low unit price.

In computer programming, assembly language (or assembler language), is any low-level programming language in which there is a very strong correspondence between the instructions in the language and the architecture's machine code instructions. Because assembly depends on the machine code instructions, every assembly language is designed for exactly one specific computer architecture. Assembly language may also be called symbolic machine code. Assembly code is converted into executable machine code by a utility program referred to as an assembler. The computational step when an assembler is processing a program is called assembly time.

This book is designed to be a comprehensive and easily accessible book covering the basic concepts of microprocessor and assembly language programming. It will help readers to understand the basics of microprocessor, Intel Pro-Pentium, Motorola 68000 series, DEC Alpha, PowerPC, RISC & CISC architecture, basic microprocessor architecture and interface, bus architecture, memory and Input/Output interface, register organization of 8086, memory addressing and instruction formats, memory interfacing, cache memory and cache controllers, 8255 programmable interface, 8254 programmable timer, 8251 programmable/communication interface, interrupts, 8259 programmable interrupts controller, 8086 assembly language programming, and machine coding and programs.

The book is divided into five units that follow the Self-Instruction Mode (SIM) with each unit beginning with an Introduction to the unit, followed by an outline of the Objectives. The detailed content is then presented in a simple but structured manner interspersed with Check Your Progress to test the student's understanding of the topic. A Summary along with a list of Key Terms and a set of Self-Assessment Questions and Exercises is also provided at the end of each unit for understanding, revision and recapitulation.

NOTES

# UNIT 1 INTRODUCTION TO MICROPROCESSOR

#### Structure

- 1.0 Introduction

- 1.1 Objectives

- 1.2 Introduction to Microprocessor 1.2.1 Evolution of Microprocessors

- 1.2.2 Performance of a Microprocessor

- 1.3 Overview of Intel Pro-Pentium

- 1.4 Motorola 68000 Series

- 1.5 Introduction to DEC Alpha

- 1.6 PowerPC

- 1.7 RISC & CISC Architecture

- 1.8 Answers to 'Check Your Progress'

- 1.9 Summary

- 1.10 Key Terms

- 1.11 Self-Assessment Questions and Exercises

- 1.12 Further Reading

# **1.0 INTRODUCTION**

The microprocessor is the biggest invention of the 20th century, which has changed the strengths and capabilities of the modern computer and, in particular, the personal computer. The microprocessor is the brain of any computer. The Central Processing Unit (CPU) is an electronic device which can fetch and execute a set of instructions, carry out arithmetic and logical operations and can control the input/output devices. A central processing unit, fabricated on a single chip of semiconductor is called microprocessor.

The microprocessor has travelled a long journey from the 4-bit device to the present-day 64-bit architecture. There are a number of companies manufacturing microprocessors, with the Intel Corporation governing the world. Most of the people today are more familiar with the Intel microprocessors rather than other microprocessors. The DEC Alpha, also known as the Alpha AXP, was a 64-bit RISC microprocessor originally developed and fabricated by digital equipment corp. PowerPC is a microprocessor architecture that was developed jointly by Apple, IBM, and Motorola in early 1990. The PowerPC employs Reduced Instruction Set Computing (RISC). Two paradigms of the microprocessor design are very common depending upon the complexity of the instructions and these are referred to as the CISC and RISC paradigms.

In this unit, you will study about the introduction to microprocessor, overview of Intel Pro-Pentium, Motorola 68000 series, and significance of DEC alpha, PowerPC, RISC and CISC architecture.

NOTES

### **1.1 OBJECTIVES**

After going through this unit, you will be able to:

- Understand the basics of microprocessor

- Explain the overview of Intel Pro-Pentium

- Discuss about the Motorola 68000 series

- Explain the significance of DEC alpha

- Analyse the PowerPC

- Define the RISC and CISC architecture

# **1.2 INTRODUCTION TO MICROPROCESSOR**

A microprocessor is a computer processor where in the data processing logic and control is included on a single integrated circuit, or a small number of integrated circuits. The microprocessor contains the arithmetic, logic, and control circuitry required to perform the functions of a computer's central processing unit. The integrated circuit is capable of interpreting and executing program instructions and performing arithmetic operations. The microprocessor is a multipurpose, clockdriven, register-based, digital integrated circuit that accepts binary data as input, processes it according to instructions stored in its memory, and provides results (also in binary form) as output.

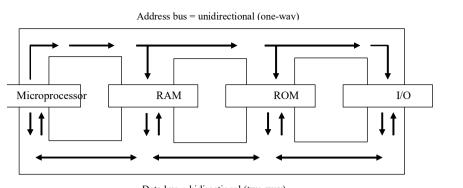

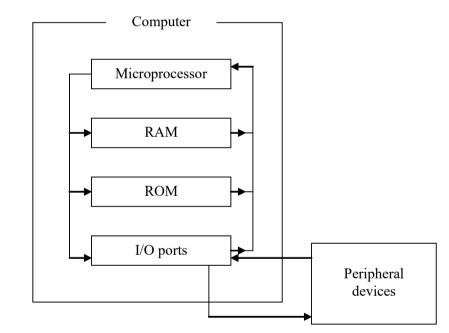

#### What is a Computer?

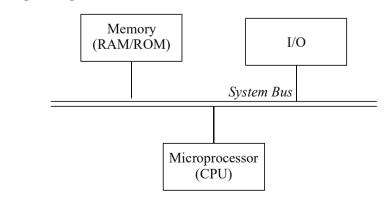

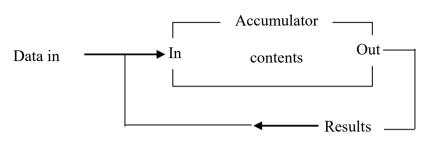

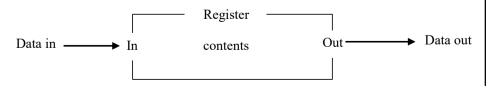

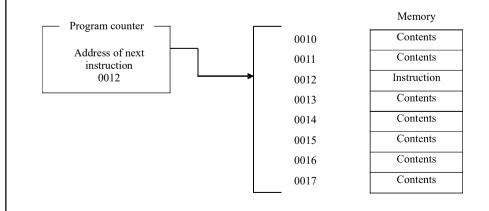

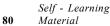

A computer is an electronic device, operating under the control of instructions (software) stored in its own memory unit, which can accept data (input), manipulate data (process) and produce information (output) from the processing. Generally, the term is used to describe a collection of devices that function together as a system. The essential components of a computer (Refer Figure 1.1) are:

- 1. System Bus

- 2. Microprocessor

- 3. Memory Unit

- 4. Input/Output Unit

Self - Learning Material

4

Fig. 1.1 Components of a Computer

NOTES

#### The System Bus

The system bus is basically a collection of signal paths which are used to carry the electrical signals across different parts of the computer. This is further divided into,

- Address Bus

- Data Bus

- Control Bus

They together connect the microprocessor to each of memory and I/O (Input/ Output) elements, which facilitates the information transformation between them.

#### Microprocessor

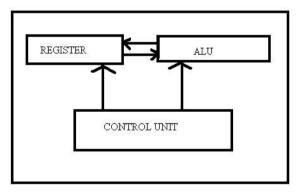

The microprocessor is the brain of any computer. Technically defining, a CPU (Central Processing Unit) fabricated on a single chip is termed as microprocessor. The CPU is an electronic device which can fetch and execute a set of instructions, carry out arithmetic and logical operations and can control the input/output devices. The microprocessor is fabricated on a single chip using MOS (Metal–Oxide–Semiconductor) technology. It comprises of the following components:

- (i) Register Unit

- (ii) Arithmetic and Logical Unit

- (iii) Timing and Control Unit

#### **Memory Organization**

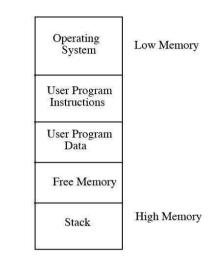

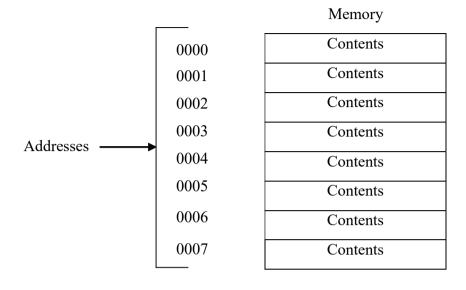

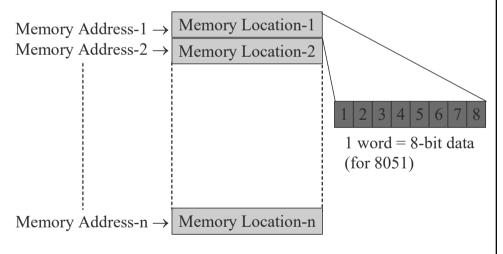

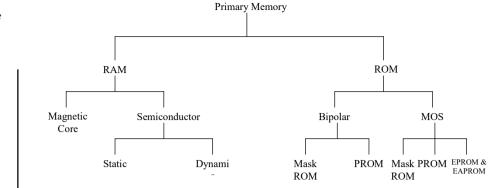

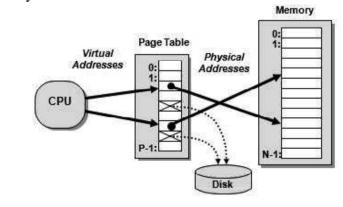

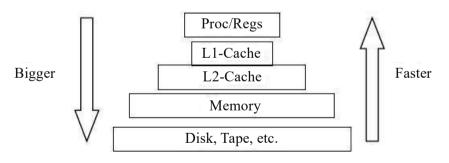

The memory unit is an integral part of any microcomputer system and its primary purpose is to hold program and data. The major goal of the memory unit is to allow it to operate at a speed close to that of the processor. The cost factor inhibits the design of the entire memory unit with single technology that guarantees high speed. In order to seek a trade-off between the cost and operating speed, the memory system is usually designed with different technologies, such as solid state, magnetic and optical. In a broad sense, a microcomputer memory can be logically divided into following three groups:

- (i) Processor Memory

- (ii) Primary or Main Memory

- (iii) Secondary Memory

#### Input/Output (I/O)

The microcomputer system communicates with the outside world via the I/O devices interfaced to it. The user can enter the program and data using the keyboard on the terminal and execute the program to obtain the results. Thus, I/O devices provide the efficient means of communication between the computer and the outside world. I/O devices are commonly called peripherals and include keyboard, CRT (Cathode Ray Tube) display, printers, disks, etc. The characteristics of I/O devices are normally different from those of the microcomputer. For example, the speed of operation of peripherals is usually slower than that of the microcomputer.

Introduction to Microprocessor

#### NOTES

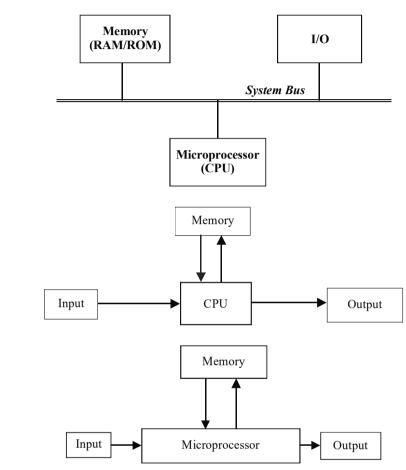

#### **Digital Computer vs Microcomputer**

The organization of I/O devices create a difference between a digital computer and a microcomputer. A computer which has the microprocessor as a CPU is called as a microcomputer. The analogy is illustrated in Figure 1.2.

Fig. 1.2 Microcomputer Versus Digital Computer

### **1.2.1 Evolution of Microprocessors**

Similar to the five generations of computers, the years of development of microprocessors can also be divided into five generations.

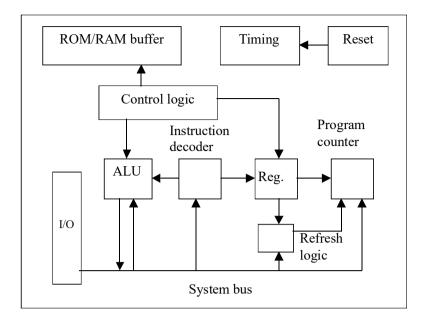

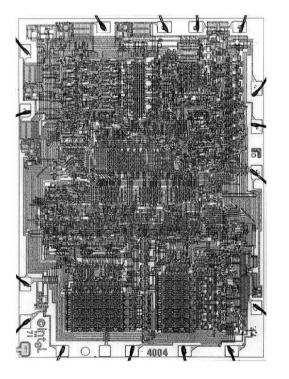

#### First Generation (1971–1973)

Intel Corporation introduced 4004, the first microprocessor, in 1971. It is evolved from the development effort while designing a calculator chip. The block diagram of Intel 4004 is shown in Figure 1.3. The layout of 4004 is shown in Figure 1.4.

Fig. 1.3 Block Diagram of Intel 4004

Fig. 1.4 Layout of 4004

The microprocessor 4004 was very successful in the calculator market at that time. However, there were three other microprocessors in the market during the same period:

- Rockwell International's PPS-4 (4 bits)

- Intel's 8008 (8 bits)

- National Semiconductor's IMP-16(16 bits)

Introduction to Microprocessor

### NOTES

NOTES

They were fabricated using PMOS (P-Channel Metal–Oxide– Semiconductor) technology, which provided low-cost, slow-speed and low-output currents. However, because of the technology, they were not compatible with TTL (Time to Live).

#### Second Generation (1974–1978)

The second generation, in fact, marked the beginning of very efficient 8-bit microprocessors. Some of the popular processors were:

- Motorola's 6800 and 6809

- Intel's 8085

- Zilog's Z80

They were manufactured using NMOS (N-Channel Metal–Oxide– Semicondcutor) technology. This technology offered faster speed and higher density than PMOS and also they were made to be TTL compatible. TTL was more common at that time.

#### Third Generation (1979–1980)

This age of microprocessors is dominated by 16-bit microprocessors. Some of them were:

- Intel's 8086/80186/80286

- Motorola's 68000/68010

They were designed using HMOS technology. HMOS (High–Performance Metal–Oxide–Semiconductor) provides some advantages over NMOS as Speed-power–product of HMOS is four times better than that of NMOS. This can also accommodate twice the circuit density compared to NMOS. Intel used HMOS technology to recreate 8085A and named it as 8085AH with a higher price tag.

#### Fourth Generation (1981–1995)

The fourth generation of microprocessors came really as a boon to the computing environment. This era marked the beginning of 32-bit microprocessors:

- Intel introduced 432, which was a tittle problematic.

- Then, a clean 80386 was launched.

- Motorola introduced 68020/68030.

They were fabricated using a low-power version of the HMOS technology called HCMOS.

Motorola introduced 32-bit RISC processors called MC88100, during the same time.

#### Fifth Generation (1995–Till Date)

The fifth generation includes chips that carry on-chip functionalities and improvements in the speed of memory and I/O devices along with introduction of 64-bit microprocessors. Intel leads the show here with Pentium, Celeron and very recently dual and quad core processors working at up to 3.5 GHz speed. A number of processors have been specifically launched for the wireless systems,

with advances in the wireless technology. The growth of microprocessors is basically the result of VLSI (Very Large Scale Integration) Technology, because of which the actual size of the chip has shrunk with the integration of so many numbers of transistors on the same chip. The growth of VLSI technology has been listed as follows:

- Vacuum tube: 1946–1957

- Transistor: 1958–1964

- Small-scale integration: 1965 onwards

- Up to 100 devices on a chip

- Medium-scale integration: till 1971

- -100-3000 devices on a chip

- Large scale integration: 1971–1977

- -3000-100,000 devices on a chip

- Very large scale integration: 1978–1991

- -100,000-100,000,000 devices on a chip

- Ultra large scale integration: 1991-present

- Over 100,000,000 devices on a chip

#### Transistors

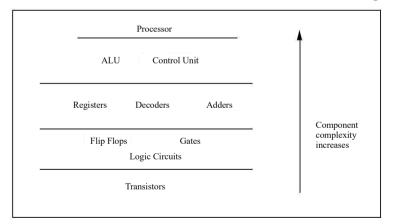

Transistors are the fundamental components from which **logic circuits** are constructed. These logic circuits are, in turn, the basic building blocks of the CPU. They include devices called **gates** and **flip-flops**. (A single gate may use up to six transistors). Gates and flip-flops are used to construct more complex circuits, such as **adders**, **decoders**, **registers** and **counters**. These circuits, in turn, are used to build **ALUs** and **control units**, i.e., CPUs, as illustrated in Figure 1.5.

Fig. 1.5 Circuits Buildings ALU and Control Units

Let us understand the circuits and components by way of analogy. Houses are made up of rooms, rooms are made up of walls, walls are made up of bricks and bricks are made up of sand and cement. If, by analogy, houses correspond to CPUs, then the sand and cement correspond to transistors. In one sense, this analogy is quite appropriate since transistors are developed on silicon chips and silicon is essential element of computer chip.

Self - Learning Material

9

Introduction to Microprocessor

#### NOTES

NOTES

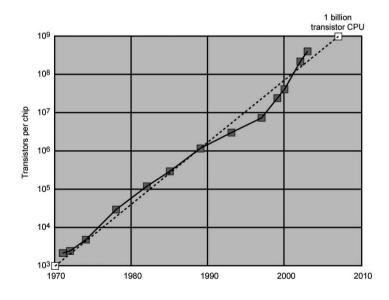

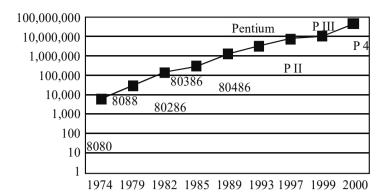

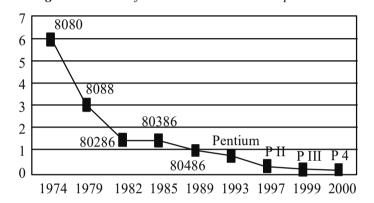

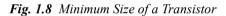

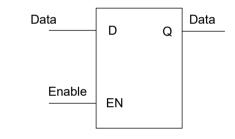

Different names are used for the basic logic circuits, such as binary circuits, digital circuits, Boolean circuits and gates. They are called logic circuits because they perform the logic operations (e.g. AND, OR, etc.). There are a number of logic gates, such as AND, OR, XOR, NAND and NOR. The term gate refers to the fact that they act like gates, letting some signals through and blocking others, depending on their inputs. The term Boolean comes from George Boole, the originator of Boolean Algebra. Logic circuits fall into two classes: sequential logic circuits and combinatorial logic circuits. Combinatorial circuits are those where the output is at all times a function of the current inputs to the circuits (no feedback is allowed from the outputs to the inputs). Decoders and adders are important examples of such circuits, which are used in the construction of digital systems such as CPUs. Sequential circuits are those where the outputs depend on past inputs as well as current inputs (they allow feedback). They are sequential in that the output depends on the sequence leading to the present situation. As a consequence, such circuits exhibit memory, i.e., they can retain information. The flip-flop is one of the best known sequential circuits. There are various of types of flip-flops such as the RS flip-flop, JK flip-flop and D-type flip-flops. Registers can be constructed from D-type flip-flops and so D-type flip-flops are commonly used in computers. Memory may also be implemented using flip-flops, as may be shift registers and counters, which are also important computer components. In short, gates and flip-flops, which are constructed out of transistors, are the basic building blocks of computers. If you see advances in the digital electronics, it is because the density of the transistors on the chips has increased drastically as shown in Figure 1.6. Similarly, the other advancements have been illustrated in Figures 1.7, 1.8, 1.9 and 1.10.

Fig. 1.6 Density of Transistors on Chips

Self - Learning Material

Introduction to Microprocessor

NOTES

# 11

#### 1.2.2 Performance of a Microprocessor

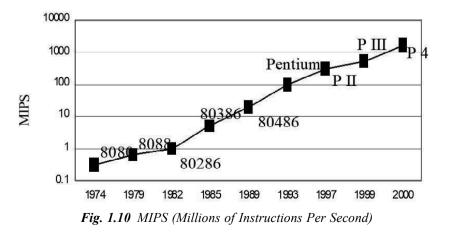

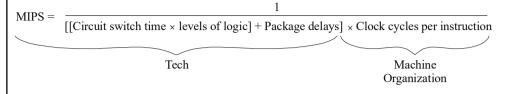

The performance of a microprocessor is most commonly measured in terms of MIPS previously, i.e. Million Instructions Per Second. The range of this rating for different microprocessors of Intel have been shown; however, technically, the MIPS is defined as follows:

#### How Can We Make Computers Work Faster?

#### The Fetch-Execute Cycle and Pipelining

The fetch–execute cycle represents the fundamental process in the operation of the CPU; attention has been focused on ways for making it more efficient. One possibility is to improve the speed at which instructions and data may be retrieved from memory, since the CPU can process information at a much faster rate than it can retrieve it from memory. Another way of improving the efficiency of the fetch–execute cycle is to use a system known as **pipelining**.

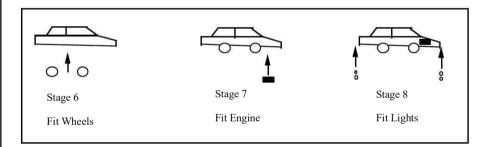

The basic idea here is to break the fetch–execute cycle into a number of separate stages, so that when one stage is being carried out for a particular instruction, the CPU can carry out another stage for a second instruction, and so on. This idea originates from the **assembly line** concept used in manufacturing industry. Consider a simplified car manufacturer's assembly line as shown in Figure 1.11.

Fig. 1.11 A Simplified Car Manufacturer's Assembly Line

The production of a car involves a number of stages, three of which are illustrated. So, for example, if a car goes through 10 stages before being completed, then you can have up to ten cars being operated on at the same time on the assembly line. If, for the sake of simplicity, you assume that each stage takes one hour to complete, then it will take 10 hours to complete the first car since it will be processed for 1 hour at every stage on the assembly line. However, when the first car has moved to the second stage of the assembly line, you can start work on a second car at the first stage of the assembly line. When the first car moves on to the third stage, the second car can move on to the second stage and a third car can be started on the first stage of the assembly line. This process continues, so

NOTES

that when the first car reaches the 10th and final stage, there are 9 other cars in the nine stages of production. This means that when the first car is finished after 10 hours, then another car will be completed every hour thereafter.

The great advantage of assembly line production is the increase in throughput that is achieved. After the first car is completed, you continue production with a throughput of one car per hour. If you did not use an assembly line and worked on one car at a time, each car would take 10 hours to be completed and the throughput would be one car per 10 hours. For example, the time taken to complete 20 cars on the assembly line is 29 hours, while without using the assembly line, the time taken would be 200 hours. It should be noted that in the assembly line, each car still requires 10 hours of processing, i.e., it still takes 10 hours of work to produce a car, the point is that because you are doing the work in stages, you can work on 10 cars at the same time, i.e., in parallel.

#### Flowthrough Time

The time taken for all stages of the assembly line to become active is called the flowthrough time, i.e., the time for the first car to reach the last stage. Once all the assembly line stages are busy, you achieve maximum throughput. You have simplified the analysis of the assembly line and, in particular, the assumption that all stages take the same amount of time is not likely to be true. The stage that takes the longest time to complete creates a bottleneck in an assembly line. For example, if you assume that stage 5 in our car assembly line takes 3 hours then the throughput decreases to 1 car per 3 hours. This is because stage 6 must wait for 3 hours before it can begin and this delay is passed on to the remaining stages, slowing the time to complete each car to 3 hours.

#### **Clock Period**

You can express this by saying the **clock period** of the assembly line (time between completed cars) is 3 hours. The clock period, denoted by  $T_p$ , of an assembly line is given by the formula:

$T_{n} = \max(t_{1}, t_{2}, t_{3}, t_{i}, \dots, t_{n})$  for  $i = 1, \dots n$

where  $t_i$  is the time taken for the *i*th stage and there are *n* stages in the assembly line. This means that the clock period is determined by the time taken by the stage that requires the most processing time. In a non-assembly line system, the total time *T*, taken to complete a car, is the sum of the time for the individual stages, i.e.,

$$T = t_1 + t_2 + t_3 + \dots + t_n$$

In our example, if all stages take 1 hour to complete, then T = 10 hours; it takes 10 hours to complete every car. If stage 5 takes 3 hours and the other stages take 1 hour to complete, then T rises to 12 hours and it will take 12 hours to complete every car.

#### Throughput

You can define the **throughput** of an assembly line to be  $1/T_p$ . Using this definition, the throughput for our assembly line where all stages take 1 hour is 1/1, i.e., 1 car/hour. If you assume that stage 5 takes 3 hours to complete, the throughput falls

Introduction to Microprocessor

#### NOTES

to 1/3 or .333 cars/hour. For non-assembly line production, the respective throughputs are 1/10 or cars/hour and 1/12 or .083 cars/hour.

#### Pipelining

Introduction to

Microprocessor

NOTES

The same principle as that of the assembly line can be applied to the fetch–execute cycle of a processor, where you refer to it as pipelining. Earlier, the fetch–execute cycle was described as consisting of three stages, which are repeated continuously:

- 1. Fetch an Instruction

- 2. Decode the Instruction

- 3. Execute the Instruction

Assuming each stage takes one clock cycle, then in a non-pipelined system, for the first instruction 3 cycles are used, followed by 3 cycles for the second instruction, and so on, (as illustrated in Figure 1.12).

|               | cycle 1 | cycle 2 | cycle 3 | cycle 4 | cycle 5 | cycle 6 |

|---------------|---------|---------|---------|---------|---------|---------|

| Instruction 1 | Fetch   | Decode  | Execute |         |         |         |

| Instruction 2 |         |         |         | Fetch   | Decode  | Execute |

#### Fig. 1.12 Non-Pipelined System

The throughput for such a system would be 1 instruction per 3 cycles. If you adopt the assembly line principle, then you can improve the throughput dramatically. Figure 1.13 illustrates the fetch–execute cycle employing pipelining.

|               | cycle 1 | cycle 2 | cycle 3 | cycle 4 | cycle 5 | cycle 6 |

|---------------|---------|---------|---------|---------|---------|---------|

| Instruction 1 | Fetch   | Decode  | Execute |         |         |         |

| Instruction 2 |         | Fetch   | Decode  | Execute |         |         |

| Instruction 3 |         |         | Fetch   | Decode  | Execute |         |

| Instruction 4 |         |         |         | Fetch   | Decode  | Execute |

Fig. 1.13 Fetch-Execute Cycle Enforcing Pipelining

Using pipelining, the processing of instructions is as follows: while the first instruction is in the execution stage, the second instruction is in the decode stage and the third instruction is being fetched.

After 3 cycles the first instruction is completed and thereafter an instruction is completed on every cycle as opposed to a throughput of 3 cycles per instruction in a non-pipelined system. Again, as in the assembly line example, each instruction still takes the same number of cycles to complete, the gain comes from the fact that the CPU can operate on instructions in the different stages in parallel. The clock period and throughput of a pipeline are then defined for the assembly line.

Clock period  $T_p = \max(t_1, t_2, t_3, t_i)$  for  $i = 1, ..., n..., t_n$

(for an *n*-stage pipeline)

#### Throughput = $1/T_{p}$

The description is quite simplified, ignoring the fact, for example, that all stages may not be completed in a single cycle. It also omits stages that arise in practice such as an operand fetch stage, which is required to fetch an operand from memory, or a write back stage to store the result of an ALU operation in a register or in memory. In practice, pipelined systems range from 3 to 10 stages; for example, Intel's Pentium microprocessor uses a 5-stage pipeline for integer instructions. There are difficulties in pipelining that would not arise on a factory assembly line, because of the nature of computer programs. Consider the following three instructions in a pipeline:

jg label move y, 0 move x, 3 ..... label:

When the jg instruction is being executed, the following two instructions will be at earlier stages, one being fetched and the other being decoded. However, if the jg instruction evaluates the condition to be true, it means that the two move instructions will not be executed and new instructions have to be loaded, starting at the instruction indicated by label.

This means that the pipeline has to be flushed and reloaded with new instructions. The time taken to reload the pipeline is called the branch penalty and may take several clock cycles. Branch instructions occur very frequently in programs and so it is important to process them as efficiently as possible.

A technique known as branch prediction can be used to alleviate the problem of conditional branch instructions, whereby the system 'guesses' the outcome of a conditional branch evaluation before the instruction is evaluated and loads the pipeline appropriately. Depending on how successfully the guess is made, the need for flushing the pipeline can be reduced. When the branch has been evaluated, the processor can take appropriate action if a wrong guess was made. In the event of an incorrect guess, the pipeline will have to be flushed and new instructions loaded. Branch prediction is used on a number of microprocessors, such as the Pentium and PowerPC. Successful guesses ranging from 80% to 85% of the time are cited for the Pentium microprocessor. Another technique is to use delayed branching. In this case, the instruction following the conditional jump instruction is always executed. For example, if the conditional jump instruction is implementing a loop by jumping backwards, it may be possible to place one of the loop body instructions after the conditional jump instruction cannot be placed here, then a nop instruction can be used. Introduction to Microprocessor

#### NOTES

# **1.3 OVERVIEW OF INTEL PRO-PENTIUM**

NOTES

The world's first microprocessor, the Intel 4004, was a 4-bit microprocessor—a programmable controller on a chip. It addressed a mere 4096 4-bit wide memory locations. The 4004 instruction set contained only 45 instructions. It was fabricated with the then state-of-the-art p-channel MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) technology that only allowed it to execute instructions at the slow rate of 50 kips (kilo-instructions per second). This was slow when compared to the 100,000 instructions executed per second by the 30-ton ENIAC (Electronic Numerical Integrator and Computer) computer in 1946. The main difference was that the 4004 weighed much less than an ounce. The 4-bit microprocessor debuted in early video game systems and small microprocessorbased control systems. The main problems with this early microprocessor were its speed, word width and memory size. The evolution of the 4-bit microprocessor ended when Intel released the 4040, an updated version of the earlier 4004. The 4040 operated at a higher speed, although it lacked improvements in word width and memory size. Other companies, particularly Texas Instruments (TMS-1000), also produced 4-bit microprocessors. The 4-bit microprocessor still survives in low-end applications, such as microwave ovens and small control systems, and is still available from some microprocessor manufacturers. Most calculators are still based on 4-bit microprocessors that process 4-bit BCD (Binary-Coded Decimal) codes.

Later in 1971, realizing that the microprocessor was a commercially viable product, Intel Corporation released the 8008-an extended 8-bit version of the 4004 microprocessor. The 8008 addressed an expanded memory size (16k bytes) and contained additional instructions (a total of 48) that provided an opportunity for its application in more advanced systems. As engineers developed more demanding uses for the 8008 microprocessor, they discovered that its somewhat small in size, it has slow speed and its instruction set limited its usefulness. Intel recognized these limitations and introduced the 8080 microprocessor in 1973-the first of the modern 8-bit microprocessors. About six months after Intel released the 8080 microprocessor, Motorola Corporation introduced its MC6800 microprocessor. The floodgates opened and the 8080 - and, to a lesser degree the MC6800, ushered in the age of 8-bit microprocessors. Soon, other companies began to introduce their own versions of the 8-bit microprocessors. Table 1.1 lists several of these early microprocessors and their manufacturers. Of these early microprocessor producers, only Intel and Motorola continue successfully to create newer and improved versions of the microprocessor. Motorola has declined from having nearly 50% share of the microprocessor market to a much smaller share.

| Table 1.1 | Early | Microprocessors | and | Then | Manufacturers |

|-----------|-------|-----------------|-----|------|---------------|

|-----------|-------|-----------------|-----|------|---------------|

| Company                | Microprocessor |

|------------------------|----------------|

| Fairchild              | F-8            |

| Intel                  | 8080           |

| Motorola               | MC6800         |

| National Semiconductor | IMP-8          |

| Rockwell International | RPS-8          |

| Zilog                  | Z-8            |

In 1977, Intel Corporation introduced an updated version of the 8080—the **8085**. This was the first 8-bit, general-purpose microprocessor developed by Intel. Although only slightly more advanced than 8080 microprocessor, the 8085 executed instruction at an even higher speed. An addition that took 2.0  $\mu$ s (500,000 instructions per second) on the 8080 required only 1.3  $\mu$ s (769,230 instructions per second) on the 8085. The main advantages of the 8085 were its internal clock generator, internal system controller and higher clock frequency. This higher level of component integration reduced the 8085's cost and increased its usefulness. Intel has managed to sell well over 100 million units of the 8085 microprocessor, its most successful 8-bit, general-purpose microprocessor.

In 1978, Intel released the 8086 microprocessor and a year or so later, it released the 8088. Both devices are 16-bit microprocessors, which executed instructions in as little as 400 ns (2.5 MIPS, or 2.5 Million Instructions Per Second). This represented a major improvement over the execution speed of the 8085 processor. In addition, the 8086 and 8088 addressed 1 MB (Mega Byte) of memory, which was 16 times more memory than the 8085. This higher execution speed and larger memory size allowed the 8086 and 8088 to replace smaller minicomputers in many applications. The increased memory size and additional instructions in the 8086 and 8088 led to many sophisticated applications for microprocessors. Improvements to the instruction set included a multiply-anddivide instruction, which was missing on eartier microprocessors. In addition, the number of instructions increased from 45 on the 4004, to 246 on the 8085, to well over 20,000 variations on the 8086 and 8088 microprocessors. The 16-bit microprocessor evolved mainly because of the need for larger memory systems. The popularity of the Intel family was ensured in 1981, when IBM Corporation decided to use the 8088 microprocessor in its personal computer. Applications such as spreadsheets, word processors, spelling checkers and computer based thesauruses were memory intensive and required more than the 64 KB of memory found in 8-bit microprocessors to execute efficiently. The 16-bit 8086 and 8088 provided 1 MB of memory for these applications. Soon, even the 1 MB memory system proved limiting for large databases and other applications. This led Intel to introduce the 80286 microprocessor, an updated 8086, in 1983.

#### The 80286 Microprocessor

The 80286 microprocessor (also a 16-bit architecture microprocessor) was almost identical to the 8086 and 8088, except it addressed a 16 MB memory system instead of a 1 MB system. The instruction set of the 80286 was almost identical to that of the 8086 and 8088, except for a few additional instructions that managed the extra 15 MB of memory. The clock speed of the 80286 was increased, so it executed some instructions in as little as 250 ns (4.0 MIPS) with the originally released 8.0 MHz version.

#### The 32-Bit Microprocessor

Applications began to demand faster microprocessor speeds, more memory and wider data paths. This led to the arrival of the 80386 in 1986, by Intel Corporation. The 80386 represented a major overhaul of the 16-bit 8086—80286 architecture. The 80386 was Intel's first practical 32-bit microprocessor that contained a

Introduction to Microprocessor

#### NOTES

NOTES

32-bit data bus and a 32-bit memory address. Through these 32-bit buses, the 80386 addressed up to 4 GB (Giga Byte)) of memory. It can well be imagined that a 4GB memory can store 1000,000 typewritten, double-spaced pages of ASCII (American Standard Code of Information Interchange) text data. However, applications require higher microprocessor speeds and large memory systems including software systems that use a GUI (Graphical User Interface). Modern graphical displays often contain 256,000 or more picture elements (pixels, or Pels). The least sophisticated VGA (Variable Graphics Array) video display has a resolution of 640 pixels per scanning line with 480 scanning lines. To display one screen of information, each picture element must be changed, which requires a high-speed microprocessor. Many new software packages use this type of video interface. These GUI-based packages require high microprocessor speeds and accelerated video adapters for quick and efficient manipulation of video text and graphical data. The most striking system, which requires high-speed computing for its graphical display interface, is Microsoft Corporation's Windows.

The 32-bit microprocessor was in fact needed because of the size of its data bus, which transfers real (single-precision floating-point) numbers that require 32-bit wide memory. In order to efficiently process 32-bit real numbers, the microprocessor must efficiently pass them between itself and memory. If the numbers pass through an 8-bit data bus, it takes four read or write cycles; when passed through a 32-bit data bus, however, only one read or write cycle is required. This significantly increases the speed of any program that manipulates real numbers. Most High-Level Languages, spreadsheets and database management systems use real numbers for data storage. Real numbers are also used in graphical design packages that use vectors to plot images on the video screen. These include, such CAD (Computer Aided Drafting/Design) systems such as, AUTOCAD, ORCAD, and so on. Besides providing higher clocking speeds, the 80386 included a memory management unit that allowed memory resources to be allocated and managed by the operating system. Earlier microprocessors left memory management completely to the software. The 80386 included hardware circuitry for memory management and memory assignment, which improved its efficiency and reduced software overhead. The instruction set of the 80386 microprocessor was compatible with the earlier 8086, 8088 and 80286 microprocessors.

#### The 80486 Microprocessor

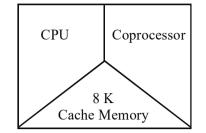

In 1989, Intel released the 80486 microprocessor, which incorporated an 80386like microprocessor, an 80387-like numeric coprocessor (for real mathematical calculations), and an 8 kB cache memory system into one integrated package. Although the 80486 microprocessor was not radically different from the 80386, it did include one substantial change—the internal structure of the 80486 was modified from the 80386 so that about half of its instructions were executed in one. The architectural concept is illustrated in Figure 1.14.

#### NOTES

Fig. 1.14 Architectural Concept of 80486 Microprocessor

#### **The Pentium Microprocessor**

The Pentium, introduced in 1993, was similar to the 80386 and 80486 microprocessors. This microprocessor was originally labeled P5 or 80586, but Intel decided not to use a number because it appeared to be impossible to copyright a number. The two introductory versions of the Pentium operated with a clocking frequency of 60 MHz and 66 MHz. The double-clocked Pentium, operating at 120 MHz and 133 MHz, was also available, as were higher-speed versions. (The fastest version produced by Intel is the 233 MHz Pentium, which is a three and a half clocked version.) Another difference was that the cache memory size was increased to 16 kB from the 8 kB cache found in the basic version of the 80486. The Pentium contained an 8 kB instruction cache and an 8 kB data cache, which allowed a program that transfers a large amount of memory data to still benefit from a cache. The memory system contained up to 4 GB, with the data bus width increased from the 32 bits found in the 80386 and 80486 to a full 64 bits. This wider data bus width accommodated double-precision floating-point numbers used for modern high-speed, vector-generated graphical displays. These higher bus speeds allowed virtual reality software to operate at more realistic rates on current and future Pentium-based platforms. The widened data bus and higher execution speed of the Pentium allow full-frame video displays to operate at scan rates of 30 Hz or higher-comparable to commercial television. Recent versions of the Pentium also included additional instructions, called multimedia extensions, or MMX instructions. Although Intel hoped that the MMX instructions would be widely used, it appears that few software companies have used them.

#### **Pentium Pro Processor**

A recent entry from Intel is the Pentium Pro processor, formerly codenamed the P6 microprocessor. The Pentium Pro processor contains 21 million transistors, 3 integer units, as well as a floating-point unit to increase the performance of most software. The basic clock frequency was 150 MHz and 166 MHz in the initial offering made available in late 1995. In addition to the internal 16K Level-one (L 1) cache (8k for data and 8k for instructions), the Pentium Pro processor also contains a 256k Level-two (L2) cache. One other significant change is that the Pentium Pro processor uses three execution engines, so it can execute up to three instructions at a time, which can conflict and still execute in parallel. This represents a change from the Pentium, which executes two instructions simultaneously as long as they do not conflict. The Pentium Pro microprocessor has been optimized to efficiently execute 32-bit code; for this reason, it is often bundled with Windows NT rather than with normal versions of Windows 95. Intel launched the Pentium

Pro processor for the server market. Still another change is that the Pentium Pro can address either a 4 GB memory system or a 64 GB memory system. The Pentium Pro has a 36-bit address bus if configured for a 64 GB memory system.

NOTES

#### | Pentium II and Pentium II Xeon Microprocessors

The Pentium II microprocessor (released in 1997) represents a new direction for Intel. Instead of being an integrated circuit as with prior versions of the microprocessor, Intel has placed the Pentium II on a small circuit board. The main reason for the change is that the L2 cache found on the main circuit board of the Pentium was not fast enough to justify a new microprocessor. On the Pentium system, the L2 cache operates at the system bus speed of 60 MHz or 66 MHz. The L2 cache and microprocessor are on a circuit board called the Pentium II module. This on-board, L2 cache operates at a speed of 133 MHz and stores 512K bytes of information. The microprocessor on the Pentium II module is actually a Pentium Pro with MMX extensions, which has no internal L2 cache.

In 1998, Intel changed the bus speed of the Pentium II. Because the 266 MHz through the 333 MHz Pentium II microprocessors used an external bus speed of 66 MHz, there was a bottleneck, so the newer Pentium II microprocessors use a 100 MHz bus speed. The Pentium II microprocessors rated at 350 MHz, 400 MHz and 450 MHz all use this higher 100 MHz memory bus speed. The higher speed memory bus requires the use of 8 ns SDRAM in place of the 10 ns SDRAM found in use with the 66 MHz bus speed.

In mid-1998 Intel announced a new version of the Pentium II called the Xeon, which was specifically designed for high-end workstation and server applications. The main difference between the Pentium II and the Pentium II Xeon is that the Xeon is available with a L1 cache size of 32K bytes and a L2 cache size of either 512K, 1M, or 2M bytes. This newer product represents a change in Intel's strategy: Intel now produces a professional version and a home/ business version of the Pentium II microprocessor.

#### Pentium III Microprocessor

The Pentium III microprocessor uses a faster core than the Pentium II, but it is still a P6 or Pentium Pro processor. It is also available in the slot 1 version mounted on a plastic cartridge and a socket 370 version called a flip-chip, which looks like the older Pentium package. Intel claims the flip-chip version costs less. Another difference is that the Pentium III is available to clock frequencies of 1 GHz. The slot 1 version contains a 512k cache and the flip-chip version contains a 256k cache. The speeds are comparable because the cache in the slot 1 version runs at one-half the clock speed, while the cache in the flip-chip version runs at the clock speed. Both versions use a memory bus speed of 100 MHz, while the Celeron uses a memory bus clock speed of 66 MHz.

#### Pentium 4 Microprocessor

The Pentium 4 microprocessor, the latest Intel release, was first available in late 2000. The Pentium 4, like the Pentium Pro through the Pentium III (PIII), uses

the Intel P-6 architecture. The main difference is that the Pentium 4 is available in 1.3, 1.4 and 1.5 GHz-speed version, and the chipset that supports Pentium 4 uses the RAMBUS memory technology in place of SDRAM technology. These higher microprocessor speeds are made available by an improvement in the size of the internal integration. It is also interesting to note that Intel has changed the level 1 cache size from 32 kB to 8 kB. Research must have shown that this size is large enough for the initial release version of the microprocessor, with future versions possibly containing a 32k L1 cache. The level 2 cache remains at 256 kB as in the PIII coppermine version. Another change you are likely to see is a shift from aluminium to copper interconnections. Because copper is a better conductor, it should increase the clock frequencies for the microprocessor. This is especially true now that a method for using copper has surfaced. You may also see the front side bus speed increase from the current maximum of 133 MHz to 200 MHz or higher. Finally the dual core processors are now available in the market with doubling the accumulator units and hence the processing capacity with the 32 bit microprocessors. At the same time 64 bit microprocessors are also available in the market. A complete evolution of the Intel Microprocessors can be understood by the following data:

- 8080

- First general purpose microprocessor

- 8 bit data path

- Used in first personal computer-Altair

- **8086**

- Much more powerful

- 16 bit

- Instruction cache, prefetch few instructions

- 8088 (8 bit external bus) used in first IBM PC

- 80286

- 16 MB memory addressable

- Up from 1MB

- **80386**

- 32 bit

- **80486**

- Sophisticated powerful cache and instruction pipelining

- Built in maths co-processor

- Pentium

- Superscalar

- Multiple instructions executed in parallel

- Pentium Pro

- Increased superscalar organization

- Aggressive register renaming

- Branch prediction

Introduction to Microprocessor

#### NOTES

- Data flow analysis

- Speculative execution

- Support for multitasking

NOTES

- MMX technology

- Graphics, video & audio processing

- Pentium III

Pentium II

- Additional floating point instructions for 3D graphics

- Pentium 4

- Note Arabic rather than Roman numerals

- Further floating point and multimedia enhancements

- Itanium

- 64-bit Microprocessor

- Itanium 2

- Hardware enhancements to increase speed

# 1.4 MOTOROLA 68000 SERIES

About six months after Intel released the 8080 microprocessor, Motorola Corporation introduced its MC6800 microprocessor. The floodgates opened and the 8080—and, to a lesser degree the MC6800—ushered in the age of the microprocessor. This was the first microprocessors from Motorola with all 8-bit devices (8-bit data bus). The 6800 appeared in 1975 with a clock frequency of 2 MHz and capable of addressing 64 kB of memory with a 16-bit address bus. It was somewhat similar to Intel 8080. The main architectural features of 6800 are:

- 1. The 6800 is a standard '8-bit' 2's complement microprocessor, like the Intel 8080.

- 2. The 6800 had a 16-bit stack pointer, so the stack can be located anywhere and can grow to any length up to the size of the memory.

- 3. Like the 8080, the 6800 supports multi-precision arithmetic using a carry flag and the ADC (Add with Carry) and SBC (Subtract with Carry) instructions.

- 4. Arithmetic instructions set the usual 2's complement flags: sign, zero, overflow and carry.

- 5. Unlike the 8080, the 6800 had no special purpose I/O instructions.

- 6. The 6800 had indexing, which allowed it to directly support data structures.

- 7. The 6800 had four addressing modes: immediate, indexed, extended and direct (or zero-page).

Then, there were different variations of 6800 with little modifications in memory. Finally the era of Motorola 68000 came, which is the first 16/32-bit CISC microprocessor from Motorola. Introduced in 1979 with HMOS technology

as the first member of the successful 32-bit 68k family of microprocessors, it is generally software forward compatible with the rest of the line despite being limited to a 16-bit wide external bus. After three decades in production, the 68000 architecture is still in us. The complete 6800 family shown in Table 1.2.

Table 1.2 Complete 6800 Family

Introduction to Microprocessor

#### NOTES

| Processor | Data Bus Width | Memory Size                            |  |  |  |

|-----------|----------------|----------------------------------------|--|--|--|

| 6800      | 8              | 64 kB                                  |  |  |  |

| 6805      | 8              | 2 kB                                   |  |  |  |

| 6809      | 8              | 64 kB                                  |  |  |  |

| 68000     | 16             | 16 MB                                  |  |  |  |

| 6808Q     | 8              | 1 MB                                   |  |  |  |

| 68008D    | 8              | 4 MB                                   |  |  |  |

| 68010     | 16             | 16 MB                                  |  |  |  |

| 68020     | 32             | 4GB                                    |  |  |  |

| 68030     | 32             | 4 GB + 256 cache                       |  |  |  |

| 68040     | 32             | 4  GB + 8  kB cache                    |  |  |  |

| 68050     | 32             | Proposed, but never released           |  |  |  |

| 68060     | 64             | $4 \mathrm{GB} + 16 \mathrm{kB}$ cache |  |  |  |

| PowerPC   | 64             | $4 \mathrm{GB} + 32 \mathrm{kB}$ cache |  |  |  |

Check Your Progress

- 1. What is a CPU?

- 2. Write about the different categories of microcomputer memory.

- 3. Which was the first microprocessor from Intel?

- 4. When did Intel launched Pentium?

- 5. What do you understand by MMX?

# **1.5 INTRODUCTION TO DEC ALPHA**

The **DEC Alpha**, also known as the **Alpha AXP**, was a 64-bit RISC microprocessor originally developed and fabricated by Digital Equipment Corporation (DEC), Group of Pictures (GOP) who used it in their own line of workstations and servers. Alpha, originally known as Alpha AXP, was a 64-bit Reduced Instruction Set Computer (RISC) Instruction Set Architecture (ISA) developed by Digital Equipment Corporation (DEC). It was originally designed to replace the 32-bit VAX (CISC) ISA. Digital Equipment Corporation was a pioneering American company in the computer industry. It was often referred within the computing industry as DEC (this acronym was frequently officially used by

Self - Learning Material

23

NOTES

Digital itself but the trademark was always DIGITAL). Its PDP and VAX products were the most popular minicomputers for the scientific and engineering communities during 1970s and 1980s. The highlights of the Alpha processor were:

- Typical 64-bit RISC architecture.

- Fixed instruction length.

- Five Instruction format.

- Seven-stage split integer/floating-point pipeline.

The first few generations of the Alpha chips were some of the most innovative of their time. The first version, 21064 or EV4, was the first CMOS microprocessor with high The second, 21,164 or EV5, was the first microprocessor to place a large secondary cache on chip. The third, 21,264 or EV6, was the first microprocessor to combine both high operating frequency and the more complicated out-of-order execution microarchitecture. Alpha was implemented in microprocessors originally developed and fabricated by DEC. It was used in a variety of workstations and servers, eventually forming the basis for almost all of their mid-to-upper-scale processors. Alpha supports both the OpenVMS (previously known as OpenVMS AXP) operating system and Tru64 UNIX (previously known as DEC OSF/1 AXP and Digital UNIX). Microsoft supported the processor in Windows NT until NT 4.0 came. Open source operating systems that run on the Alpha are Linux (Debian, Gentoo Linux and Red Hat Linux), BSD UNIX (NetBSD, OpenBSD and FreeBSD up to 6.x). The Alpha architecture was sold, along with most parts of DEC, to Compaq in 1998. Compaq, already an Intel customer, decided to phase out Alpha in favour of the forthcoming Intel IA-64 'Itanium' architecture, and sold all Alpha intellectual property to Intel in 2001, effectively 'killing' the product. Hewlett-Packard purchased Compaq later that same year, continuing development of the existing product line until 2004, and promising to continue selling Alpha-based systems, largely to the existing customer base, until October 2006 (later extended to April 2007).

# **1.6 POWERPC**

PowerPC is a microprocessor architecture that was developed jointly by Apple, IBM, and Motorola in early 1990. The PowerPC Employs Reduced Instruction-Set Computing (RISC). The three developing companies have made the PowerPC architecture an open standard, inviting other companies to build on it. PowerPC is an acronym, which stands for Performance Optimization with Enhanced RISC. PowerPC is mainly based upon the Power architecture of IBM. It was first used in IBM's RS/6000 workstation with its UNIX-based operating system, AIX, and in Apple Computer's Macintosh personal computers. Today, PowerPC chips are also used in diverse applications including internetworking equipment, routers, telecom switches, interactive multimedia, automotive control, and industrial robotics. PowerPC CPUs have since become popular embedded and high-performance processors. The main architectural features of the PowerPC are:

• Designed along RISC principles.

• Allows for a superscalar implementation.

- Versions of the design exist in both 32-bit and 64-bit implementations.

- Additional floating point instructions.

- A paged memory management architecture.

Developed at IBM, the Reduced Instruction-Set Computing (RISC) specifies that these simplest computer instructions are most frequently performed. Traditionally, processors have been designed to accommodate the more complex instructions. Typically, RISC performs the more complex instructions using combinations of simple instructions. The timing for the processor can then be based on simpler and faster operations, enabling the microprocessor to perform more instructions for a given clock speed.

The architecture of PowerPC provides an alternative to the popular processor architectures from Intel, including the Pentium. Microsoft has specifically build its Windows operating system which can efficiently run on Intel processors, and this widely-sold combination is sometimes termed as 'Wintel'.

The architecture of PowerPC machine includes the following components:

#### Memory

Memory consists of 8-bit bytes. Two consecutive bytes form a halfword, four bytes form a word, eight bytes form a doubleword, and sixteen bytes form a quadword. PowerPC programs can be written using a 264 bytes Virtual Address Space (VAS). Address spaces are divided into fixed-length segments which are further divided into pages.

#### Registers

There are 32 General-Purpose Registers (GPR) from GPR0 to GPR31. Length of each register is 64-bit. The general purpose register are used to store and manipulate data and addresses. As PowerPC machine support floating point data format so it have Floating-Point Unit (FPU) for computation.

Following Table 1.3 illustrates the register's supported by PowerPC architecture.

| Register                | Operations                                                 |

|-------------------------|------------------------------------------------------------|

| Link Register (LR)      | Contain address to return at the end of the function call. |

| Condition Register (CR) | Signifies the result of an instruction.                    |

| Count Register (CTR)    | Used for Loop count.                                       |

Table 1.3 Register's Supported by PowerPC Architecture

#### **Data Formats**

Integers are stored as 8-, 16-, 32-, or 64-bit Binary numbers.

Characters are represented using 8-bit ASCII (American Standard Code for Information Interchange) codes.

Floating points are represented using two different floating-point formats namely Single-precision format and double-precision format.

Introduction to Microprocessor

#### NOTES

NOTES

#### **Instruction Formats**

PowerPC support seven basic instruction formats. All of these instruction formats are 32-bits long. PowerPC architecture instruction format have more variety and complexity as compared to other RISC systems, such as SPARC (Scalable Processor ARChitecture). Bit numbering for PowerPC is the opposite of most other definitions:

- Bit 0 is the Most Significant Bit (MSB).

- Bit 31 is the Least Significant Bit (LSB).

Instructions are first decoded by the upper 6 bits in a field, called the primary opcode. The remaining 26 bits contain fields for operand specifiers, immediate operands, and extended opcodes, and these may be reserved bits or fields.

#### **Instruction Set**

PowerPC architecture is more complex than the other RISC systems. Thus PowerPC architecture has approximately 200 machine instructions. This architecture follow pipeline execution of instructions which means while one instruction is executed next one is being fetched from memory and decoded.

#### **Input and Output**

PowerPC architecture follow two different methods for performing I/O (Input/ Output) operations. In one approach Virtual Address Space (VAS) are used while in other approach I/O is performed using Virtual memory management.

Principally, the PowerPC is based on IBM's earlier POWER Instruction Set Architecture (ISA), and retains a high level of compatibility with it; the architectures have remained close enough that the same programs and operating systems will run on both if some care is taken in preparation; newer chips in the POWER series use the Power ISA.

# **1.7 RISC & CISC ARCHITECTURE**

RISC (Redced Instruction Set Computer) and CISC (Complex Instruction Set Computer)) are two architectural paradigms in the microprocessors. Each one has it own popularity and applications, obviously for different reasons. In case of mainframes, RISC has been very popular since long back. However in case of the Personal Computers, CISC is very common. Through this discussion, we will try to main aspects of both of them and then try to make a comparison.

#### CISC

Today, the CISC can be thought as a microprocessor of the common man. However there were obvious technical goals behind the development of CISC:

- 1. Before the advent of compilers, all programming was done in machine code or assembly because of the following reasons:

- (i) To make programming easier, more complex instructions were created.

- (ii) These instructions were direct representations of high level functions in high level programming languages.

- (iii) This was supposed to be a good idea, since at the time, hardware design was easier than compiler design.

- 2. Computers had very little memory at that time and hence:

- (i) This promoted a high density of information in programs.

- (ii) Instructions of variable size, instructions which perform multiple operations, and instructions that both moved data and performed data computations.

- (iii) The ability to pack instructions densely was considered more important than instruction decidability.

- 3. Register count in the processors was small, hence

- (i) Bits in registers were more expensive than external memory, and would have been difficult to include in large numbers due to technology limitations.

- (ii) More registers require more instruction bits (so all registers can be addressed)—this would take up expensive RAM.

Because of these reasons, instructions were designed to do as much work as possible.

- 1. One instruction could load up two numbers, add them, and store the result back to memory.

- 2. Another version of that instruction would do the same, but store the result in a register.

- 3. Yet another version would read one number from memory, the second from register, and write the result back to memory.

This design philosophy became known as CISC (Complex Instruction Set Computer). Pronounced *sisk*, and stands for Complex Instruction Set Computer. Most PC's use CPU based on this architecture. For instance Intel and AMD CPU's are based on CISC architectures. Typically CISC chips have a large amount of different and complex instructions. The philosophy behind it is that hardware is always faster than software, therefore one should make a powerful instruction set, which provides programmers with assembly instructions to do a lot with short programs. In common CISC chips are relatively slow (compared to RISC chips) per instruction, but use little (less than RISC) instructions.

#### RISC

With the advances in technology, CPUs started to run faster than the memory in the late 1970s. it was already apparent that CPU and memory speed would grow further apart. This development led to complete change in the architectural philosophy of microprocessors:

- 1. To support the higher CPU speeds, more registers were needed:

- (i) Additional registers would require more space on the chip.

- (ii) This space could be created by reducing the complexity of the CPU.

- 2. Real world examples showed that most processors were over-designed:

- (i) On average, 98% of the constants in a program will fit into 13 bits, while almost every CPU stored them in individual words.

Introduction to Microprocessor

#### NOTES

NOTES

- (ii) This suggests that the CPU should store the constants in unused bits of the instruction itself, decreasing the number of memory accesses.

- (iii) If this scheme is used, the operation needs to be small, so that there is enough room left in the 32 bit instruction to hold larger constants.

3. Real world programs spend most of their time executing simple operations:

- (i) Focus was put on making these common operations as simple and fast as possible.

- (ii) The goal was to make instructions so simple, each could be fully completed in a single clock cycle.

Thus, instead of a single complex instruction, code was implemented as a series of smaller instructions. This left more space in the instruction for data. The number one rule for a RISC implementation was to 'make the common case fast' Unfortunately, this also meant that the total number of instructions that needed to be read from memory for any single program is larger, and takes longer. This focus on 'Reduced Instructions' led to the result being called 'Reduced Instruction Set Computer'(RISC) pronounced risk, and stands for Reduced Instruction Set Computer. RISC chips evolved around mid-1980 as a reaction at CISC chips. The philosophy behind it is that almost no one uses complex assembly language instructions as used by CISC, and people mostly use compilers which never use complex instructions. Apple for instance uses RISC chips. Therefore fewer, simpler and faster instructions would be better, rather than the large, complex and slower instructions of CISC. However, more instructions are needed to accomplish a task. Another advantage is that RISC chips require fewer transistors, which makes them easier to design and cheaper to produce. Finally, it's easier to write powerful compilers as only few instructions are available.

#### **Check Your Progress**

- 6. Which is the latest 64-bit microprocessor from Intel?

- 7. Who developed PowerPC?

- 8. Define the term RISC.

# **1.8 ANSWERS TO 'CHECK YOUR PROGRESS'**

- 1. CPU is an electronic device which can fetch and execute a set of instructions, carry out arithmetic and logical operations and can control the input /output devices.

- 2. There are three categories of memories:

- Processor Memory

- Primary or Main Memory

- Secondary Memory

- 3. 4004 was the first microprocessor from Intel.

- 4. Intel launched Pentium in 1993.

- 5. MMX means MultiMedia Extensions; these are the instructions to support the multimedia capabilities.

- 6. Itanimum is the latest 64-bit microprocessor from Intel.

- 7. PowerPC is a microprocessor architecture that was developed jointly by Apple, IBM, and Motorola in early 1990. The Power PC employs Reduced Instruction Set Computing (RISC).

- 8. Instead of a single complex instruction, code was implemented as a series of smaller instructions. This left more space in the instruction for data. The number one rule for a RISC implementation was to 'Make the common case fast'Unfortunately, this also meant that the total number of instructions that needed to be read from memory for any single program is larger, and takes longer. This focus on 'Reduced Instructions' led to the result being called 'Reduced Instruction Set Computer' (RISC) pronounced risk, and stands for Reduced Instruction Set Computer.

# **1.9 SUMMARY**

- A computer is an electronic device, operating under the control of instructions (software) stored in its own memory unit, which can accept data (input), manipulate data (process) and produce information (output) from the processing.

- The CPU is an electronic device which can fetch and execute a set of instructions, carry out arithmetic and logical operations and can control the input/output devices.

- The memory unit is an integral part of any microcomputer system and its primary purpose is to hold program and data.

- The major goal of the memory unit is to allow it to operate at a speed close to that of the processor. The cost factor inhibits the design of the entire memory unit with single technology that guarantees high speed.

- The microcomputer system communicates with the outside world via the I/O devices interfaced to it. The user can enter the program and data using the keyboard on the terminal and execute the program to obtain the results.

- Transistors are the fundamental components from which logic circuits are constructed. These logic circuits are, in turn, the basic building blocks of the CPU.

- The fetch-execute cycle represents the fundamental process in the operation of the CPU; attention has been focused on ways for making it more efficient. One possibility is to improve the speed at which instructions and data may be retrieved from memory, since the CPU can process information at a much faster rate than it can retrieve it from memory.

- The world's first microprocessor, the Intel 4004, was a 4-bit microprocessor – a programmable controller on a chip. It addressed a mere 4096 4-bit wide memory locations.

Introduction to Microprocessor

#### NOTES

#### **NOTES**

- The 80286 microprocessor (also a 16-bit architecture microprocessor) was almost identical to the 8086 and 8088, except it addressed a 16 MB memory system instead of a 1 M B system.

- In 1989, Intel released the 80486 microprocessor, which incorporated an 80386- like microprocessor, an 80387-like numeric coprocessor (for real mathematical calculations), and an 8 KB cache memory system into one integrated package.

- The Pentium, introduced in 1993, was similar to the 80386 and 80486 microprocessors.

- PowerPC is a microprocessor architecture that was developed jointly by Apple, IBM, and Motorola in early 1990. The Power PC employs Reduced Instruction Set Computing (RISC).

- The DEC Alpha, also known as the Alpha AXP, was a 64-bit RISC microprocessor originally developed and fabricated by digital equipment corp.

- Alpha was implemented in microprocessors originally developed and fabricated by DEC. It was used in a variety of workstations and servers, eventually forming the basis for almost all of their mid-to-upper-scale processors.

- Alpha supports both the OpenVMS (previously known as OpenVMSAXP) operating system and Tru64 UNIX (previously known as DEC OSF/1 AXP and Digital UNIX).

- RISC and CISC are two architectural paradigms in the microprocessors. Each one has it own popularity and applications, obviously for different reasons. In case of mainframes, RISC has been very popular since long back. However in case of the Personal Computers, CISC is very common.

- This design philosophy became known as CISC (Complex Instruction Set Computer). Pronounced sisk, and stands for Complex Instruction Set Computer.

# 1.10 KEY TERMS

- **Computer:** A computer is an electronic device, operating under the control of its instructions stored in its own memory unit.

- System bus: The system bus is basically a collection of signal paths, which are used to carry the electrical signals across different parts of the computer.

- **CPU:** CPU is an electronic device, which can fetch and execute certain set of instructions, carry out arithmetic and logical operations, and can control the input/output devices.

- **PowerPC:** PowerPC is a microprocessor architecture that employs reduced instruction-set computing.

- **DEC Alpha:** DEC Alpha is a 64-bit RISC microprocessor originally developed and fabricated by Digital Equipment Corporation (DEC).

# 1.11 SELF-ASSESSMENT QUESTIONS AND EXERCISES

### **Short-Answer Questions**

- 1. What do you understand by the fifth-generation microprocessors?

- 2. Who developed PowerPC and why?

- 3. Define the main features of DEC Alpha.

- 4. Compare the Motorola processors with the Intel processors.

- 5. What is the technical goals behind the development of CISC?

- 6. State the need for RISC processors.

### **Long-Answer Questions**

- 1. Briefly explain the evolution of microprocessor with the help of diagram and examples.

- 2. Discuss about the Intel Pro-Pentium giving appropriate examples.

- 3. Describe the Motorola 68000 series giving examples

- 4. Briefly explain about the PowerPC and DEC Alpha.

- 5. Compare the characteristics of CISC and RISC. Which is better in terms of speed and why?

# **1.12 FURTHER READING**

- Goankar, Ramesh. 2002. *Microprocessor Architecture, Programming and Application with the 8085*. Mumbai: Penram International Publishing.

- Ram, B. 2005. *Fundamentals of Microprocessor and Microcomputers*. New Delhi: Dhanpat Rai Publications.

- Lotia, Manahar and Pradeep Nair. 2003. *Modern All About Motherboard*. New Delhi: BPB Publications.

- Mueller, Scott, and Craig Zacker. 2002. *Upgrading and Repairing PCs*. New Jersey: Pearson Education (Que Publishing).

- Godse, D.A. and A.P. Godse. 2007. Microprocessor and Assembly Language

- Programming. Pune: Technical Publications.

- Kleitz, William. 2009. Digital and Microprocessor Fundamentals: Theory and

Applications. New Jersey: Prentice Hall.

Ray, A.K. and K.M. Bhurchandi. 2000. *Advanced Microprocessors and Peripherals*. New Delhi: Tata McGraw-Hill.

Introduction to Microprocessor

NOTES

## 31

Self - Learning

Material

# UNIT 2 BASIC MICROPROCESSOR ARCHITECTURE AND INTERFACE

### Structure

- 2.0 Introduction

- 2.1 Objectives

- 2.2 Internal Architecture of Microprocessor

- 2.3 External System and Bus Architecture 2.3.1 The System Bus

- 2.4 Memory

- 2.5 Input/Output (I/O) Interface

- 2.6 Answers to 'Check Your Progress'

- 2.7 Summary

- 2.8 Key Terms

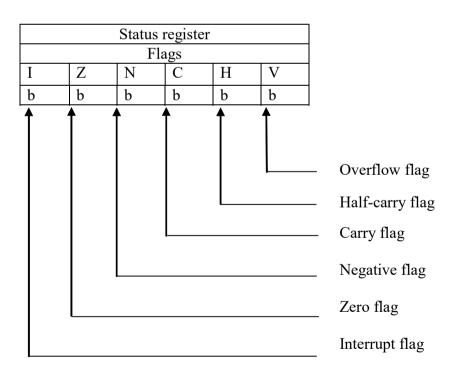

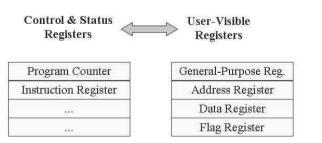

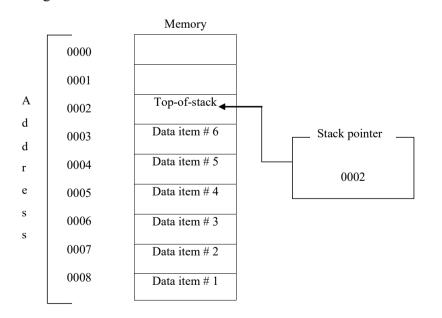

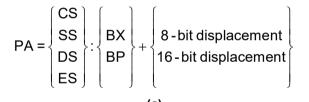

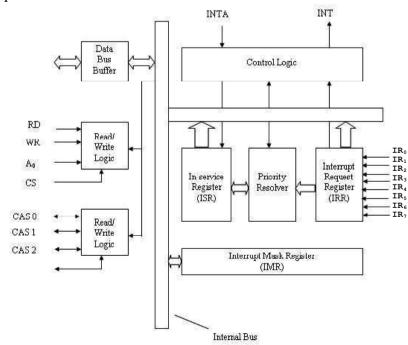

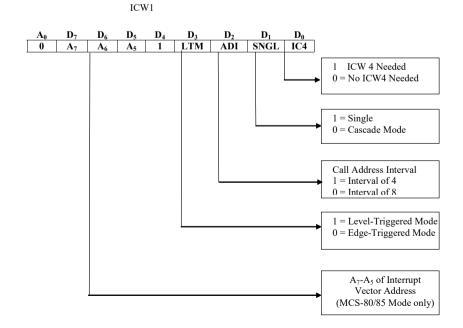

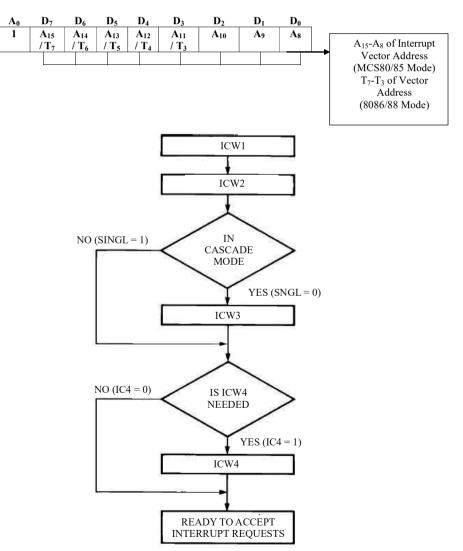

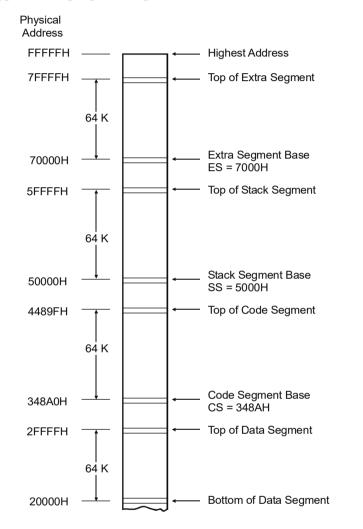

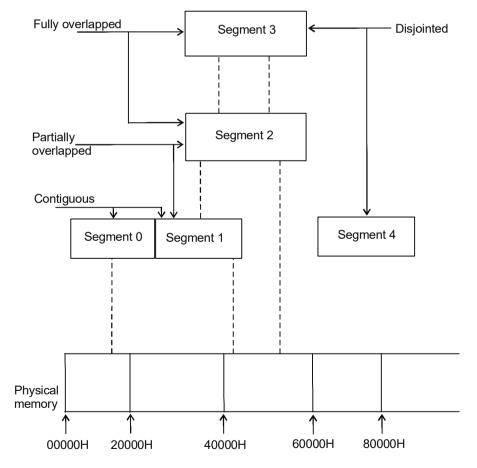

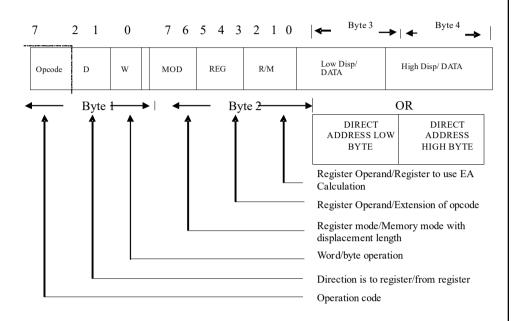

- 2.9 Self-Assessment Questions and Exercises