M. Sc. (IT) Previous Year

# **MIT-02**

# COMPUTER ORGANIZATION AND ARCHITECTURE

मध्यप्रदेश भोज (मुक्त) विश्वविद्यालय — भोपाल MADHYA PRADESH BHOJ (OPEN) UNIVERSITY - BHOPAL

**Reviewer** Committee 1. Dr. Amit Kumar Mandle 3. Dr. K. Mani Kandan Nair Assistant Professor Department of Computer Science IEHE, Bhopal Makhanlal Chaturvedi National University of Journalism & Communication, Bhopal 2. Dr. Romsha Sharma Professor Shri Sathya Sai College for Women, Bhopal Advisory Committee 4. Dr. Amit Kumar Mandle 1. Dr. Jayant Sonwalkar Assistant Professor Hon'ble Vice Chancellor IEHE, Bhopal Madhya Pradesh Bhoj (Open) University, Bhopal 5. Dr. Romsha Sharma 2. Dr. L.S. Solanki Professor Registrar Shri Sathya Sai College for Women, Bhopal Madhya Pradesh Bhoj (Open) University, Bhopal 6. Dr. K. Mani Kandan Nair 3. Dr. Kishor John Department of Computer Science Director Makhanlal Chaturvedi National University of Madhya Pradesh Bhoj (Open) University, Bhopal Journalism & Communication, Bhopal **COURSE WRITERS** B. Basavaraj, HOD, Department of Electronics & Communication Engineering, SJR College of Science, Arts and Commerce, Bangalore Units: (1.0-1.2, 1.6, 1.8-1.9, 1.11-1.16, 2.5.2-2.5.8)

Vivek Kesari, Assistant Professor, Galgotia's GIMT, Institute of Management & Technology, Greater Noida, NOIDA Units: (2.3, 2.5-2.5.1, 4.3-4.5, 4.6, 4.9.3, 4.10, 4.11)

Sanjay Saxena, Renowned Author of over 130 Books on Information Technology, New Delhi Units: (2.6, 2.7.2, 2.10-2.10.2, 2.10.5, 3.0-3.2)

**Dr Deepti Mehrotra,** Professor & Head, Accreditation, Ranking & Quality Assurance, AMITY School of Engineering and Technology, AMITY University, NOIDA

**Units:** (1.3-1.5, 1.7, 1.10, 2.0-2.2, 2.4, 2.7-2.7.1, 2.8-2.9, 2.10.3-2.10.4, 2.11-2.15, 3.2.1-3.2.5, 3.3, 3.3.1-3.3.2, 3.3.3-3.8, 4.0-4.2, 4.5.1, 4.7-4.7.1, 4.8.1-4.8.7, 4.9-4.9.2, 4.9.4-4.9.7, 4.10.1, 5.2.3-5.2.6, 5.3, 5.5-5.10)

Vikas Singhal, Senior Lecturer, JSS Academy of Technical Education (JSSATE), NOIDA Dr Deepti Mehrotra, Professor & Head, Accreditation, Ranking & Quality Assurance, AMITY School of Engineering and Technology,

AMITY University, NOIDA

Units: (4.7.2, 4.8, 4.12-4.16, 5.4)

Vikas Singhal, Senior Lecturer, JSS Academy of Technical Education (JSSATE), NOIDA Units: (5.0-5.2.2)

Copyright © Reserved, Madhya Pradesh Bhoj (Open) University, Bhopal

All rights reserved. No part of this publication which is material protected by this copyright notice may be reproduced or transmitted or utilized or stored in any form or by any means now known or hereinafter invented, electronic, digital or mechanical, including photocopying, scanning, recording or by any information storage or retrieval system, without prior written permission from the Registrar, Madhya Pradesh Bhoj (Open) University, Bhopal

Information contained in this book has been published by VIKAS<sup>®</sup> Publishing House Pvt. Ltd. and has been obtained by its Authors from sources believed to be reliable and are correct to the best of their knowledge. However, the Madhya Pradesh Bhoj (Open) University, Bhopal, Publisher and its Authors shall in no event be liable for any errors, omissions or damages arising out of use of this information and specifically disclaim any implied warranties or merchantability or fitness for any particular use.

Published by Registrar, MP Bhoj (open) University, Bhopal in 2020

Vikas<sup>®</sup> is the registered trademark of Vikas<sup>®</sup> Publishing House Pvt. Ltd.

VIKAS<sup>®</sup> PUBLISHING HOUSE PVT. LTD. E-28, Sector-8, Noida - 201301 (UP) Phone: 0120-4078900 • Fax: 0120-4078999 Regd. Office: A-27, 2nd Floor, Mohan Co-operative Industrial Estate, New Delhi 1100 44 • Website: www.vikaspublishing.com • Email: helpline@vikaspublishing.com

# SYLLABI-BOOK MAPPING TABLE

# **Computer Organization and Architecture**

| Syllabi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Mapping in Book                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Unit I<br>Information Representation: Number System, Floating Point<br>Representation, Integer Representation, Character Codes.<br>Logic Gates: Boolean Algebra, Boolean Expression Simplification, Basic<br>Building Blocks and Circuits, Combinational Circuits, Arithmetic<br>Circuits, Combinational Circuits and Sequential Circuits, Registers,<br>Counters.                                                                                                                                                                                                                                                                                                                                                                                                    | Unit-1: Information Representation,<br>Logic Gates, Boolean Algebra,<br>Circuits, Registers and Counters<br>(Pages 3-100) |

| Unit - II<br>Register Manipulations and Micro-Operations: Register Transfer,<br>Bus System, Micro-Operations.<br>Computer Organization and Design Concepts: Instruction and<br>Instruction Code, Computer Instructions, Timing and Controls,<br>Instruction Cycle, Memory Reference Instructions, Input/Output and<br>Interrupts, Complete Computer Description, Machine Language, Design<br>Control Unit.                                                                                                                                                                                                                                                                                                                                                            | Unit-2: Register, Micro-Operations<br>and Design Concepts<br>(Pages 101-159)                                              |

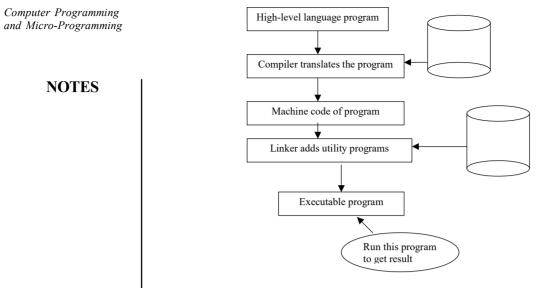

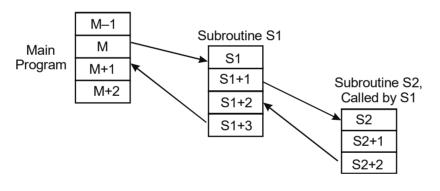

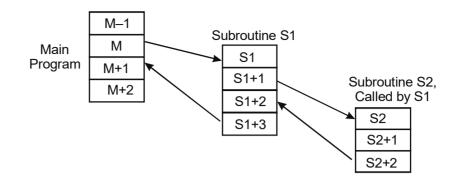

| Unit - III<br>Basic Computer Programming: Assembly Language, The Assembler,<br>Program Loops, Programming Arithmetic & Logic, Subroutines, Input/<br>Output Programming<br>Micro-Programming: Micro-Programmed Control, Address<br>Sequencing, Micro-Program Example, Design of Control Unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Unit-3: Computer Programming and<br>Micro-Programming<br>(Pages 161-217)                                                  |

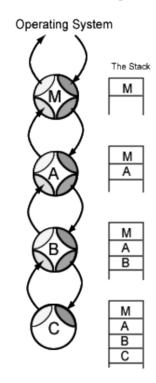

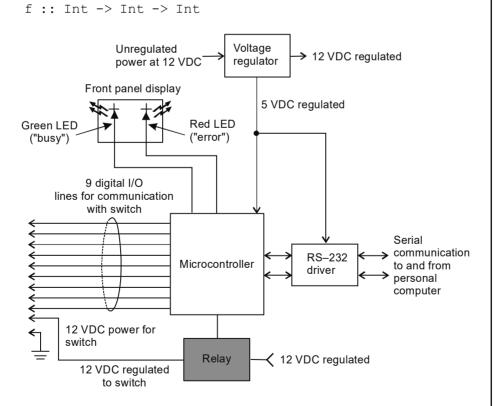

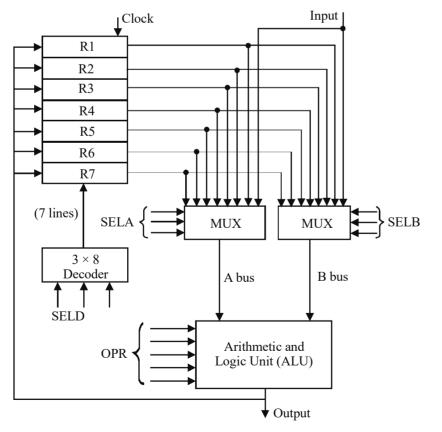

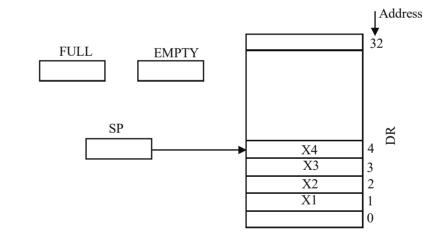

| <ul> <li>Unit - IV</li> <li>CPU Organization : Central Processing Unit, General Register</li> <li>Organization, Stack Organization, Instruction Formats, Addressing</li> <li>Modes, Data Transfer and manipulation, Micro Programmed Control,</li> <li>Reduced Instruction Set Computer</li> <li>Input-Output Organization: Peripheral Devices, Input-Output</li> <li>Interface, Asynchronous Data Transfer, Mode of Transfer, Priority</li> <li>Interrupt, Direct Memory Access (DMA), Input-Output Processor (I-OP), Serial Communication.</li> <li>Memory Organization: Memory Unit, Types of Memory, Associative</li> <li>Memory, Building Large Memories, Cache Memory, Virtual Memory,</li> <li>Parallel Processing, Methods of Parallel Processors.</li> </ul> | Unit-4: CPU, Input-Output and<br>Memory Organizations<br>(Pages 219-342)                                                  |

| Unit - V<br>Pipeline and Vector Processing : Pipeline Processing, Vector<br>Processing, Array Processing.<br>Multiprocessing : Multiprocessors, Interconnection Structure,<br>Interprocess Arbitration, Interprocessor communication and<br>synchronization, Cache Coherence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Unit-5: Pipeline, Vector Processing<br>and Multiprocessing<br>(Pages 343-422)                                             |

# CONTENTS

#### **INTRODUCTION**

# UNIT 1 INFORMATION REPRESENTATION, LOGIC GATES, BOOLEAN ALGEBRA, CIRCUITS, REGISTERS AND COUNTERS

- 1.0 Introduction

- 1.1 Objectives

- 1.2 Number System

- 1.2.1 Decimal Number System

- 1.2.2 Binary Number System

- 1.3 Floating Point Representation

- 1.3.1 Integer Representation

- 1.3.2 1's Complement Representation

- 1.3.3 2's Complement Representation

- 1.3.4 Complements

- 1.4 Character Codes

- 1.5 Logic Gates

- 1.5.1 NOT Gate

- 1.5.2 AND Gate

- 1.5.3 OR Gate

- 1.5.4 XOR Gate

- 1.6 Boolean Algebra

- 1.6.1 Logical AND Operation

- 1.6.2 Logical OR Operation

- 1.6.3 Logical Complementation (Inversion)

- 1.6.4 Basic Laws of Boolean Algebra

- 1.6.5 De Morgan's Theorems

- 1.6.6 Realization of Expression using Gates

- 1.6.7 Combinational Logic

- 1.7 Boolean Expression Simplification

- 1.7.1 Algebraic Simplification

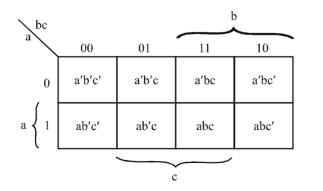

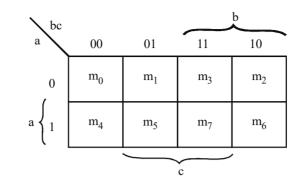

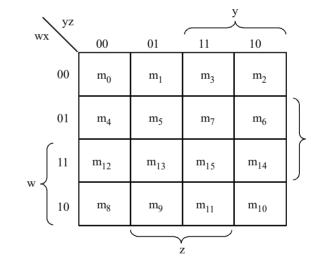

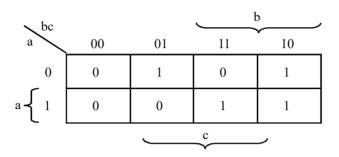

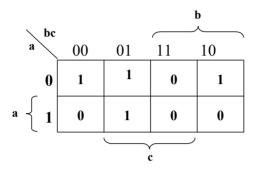

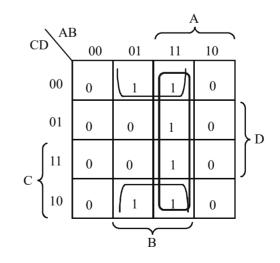

- 1.7.2 Karnaugh Map

- 1.7.3 Steps for Forming Karnaugh Map

- 1.7.4 Simplification of Expressions using Karnaugh Map

- 1.7.5 Simplification using Karnaugh Map

- 1.7.6 Simplest SOP Expressions

- 1.7.7 Getting POS Expressions

- 1.8 Combinational Circuits

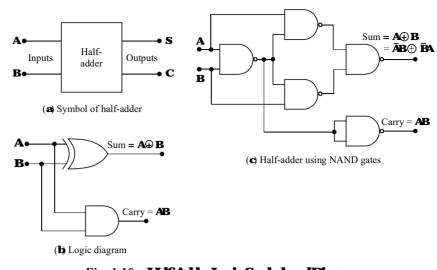

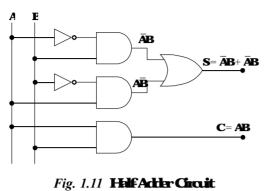

- 1.8.1 Half-Adder

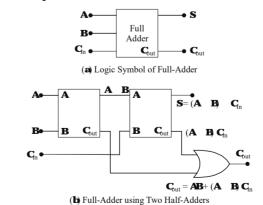

- 1.8.2 Full-Adder

- 1.8.3 Parallel Binary Adder

- 1.8.4 Subtractors

- 1.8.5 Decoders

- 1.8.6 Multiplexer

- 1.8.7 Code Converters

- 1.9 Arithmetic Circuits

- 1.9.1 Binary Addition

- 1.9.2 Binary Subtraction

- 1.9.3 Binary Multiplication

- 1.9.4 Binary Division

- 1.10 Combinational Circuits and Sequential Circuits

- 1.10.1 Analysis of a Combinational Circuit

1

3-100

#### 1.11 Registers and Counters

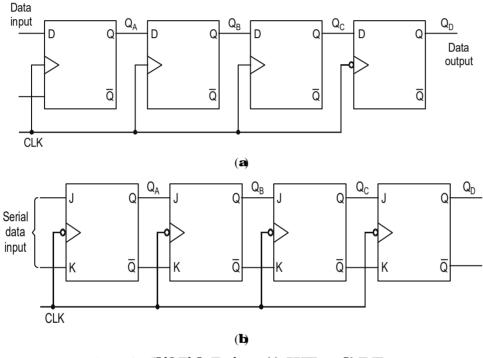

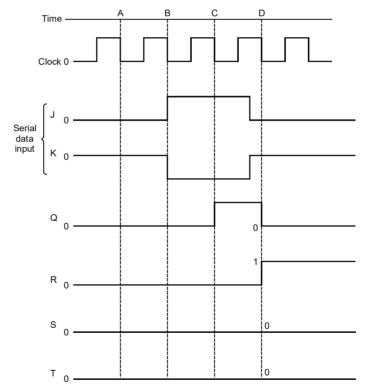

- 1.11.1 Serial-In-Serial-Out Shift Registers

- 1.11.2 Serial-In-Parallel-Out Shift Registers

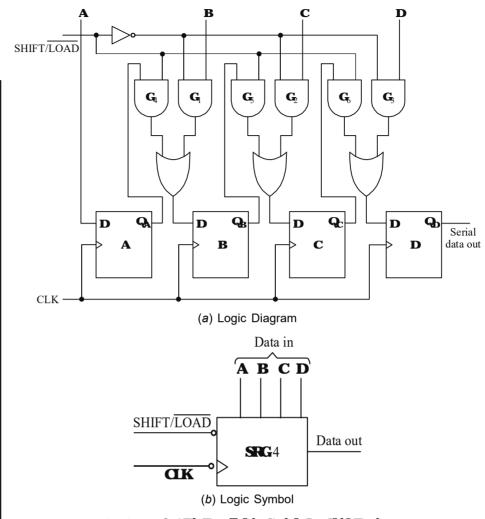

- 1.11.3 Parallel-In-Serial-Out Shift Registers

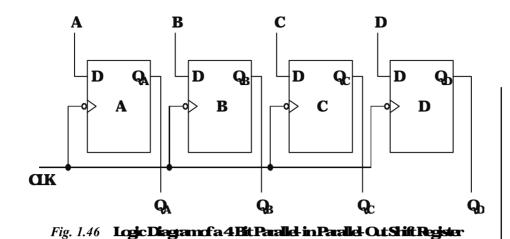

- 1.11.4 Parallel-In-Parallel-Out Registers

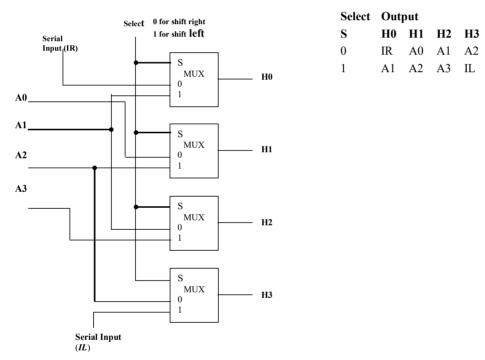

- 1.11.5 Bidirectional Shift Registers

- 1.11.6 Applications of Shift Registers

- 1.12 Answers to 'Check Your Progress'

- 1.13 Summary

- 1.17 Key Terms

- 1.15 Self-Assessment Questions and Exercises

- 1.16 Further Reading

#### UNIT 2 REGISTER, MICRO-OPERATIONS AND DESIGN CONCEPTS 101-159

- 2.0 Introduction

- 2.1 Objectives

- 2.2 Register Transfer

- 2.3 Bus System

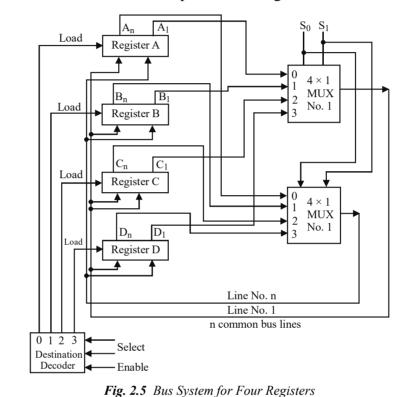

- 2.3.1 Bus Organization

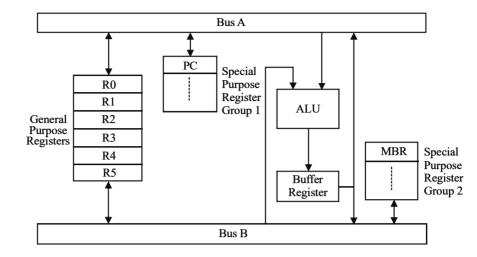

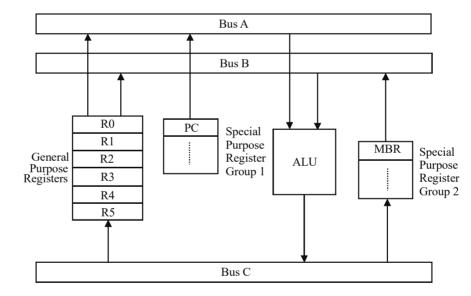

- 2.3.2 Multiple Bus Organization

- 2.4 Micro-Operations

- 2.4.1 Arithmetic Micro-Operations

- 2.4.2 Logic Micro-Operations

- 2.4.3 Shift Micro-Operations

- 2.5 Instruction and Instruction Code

- 2.5.1 Instruction Execution

- 2.5.2 Binary Coded Decimal (BCD) Code

- 2.5.3 Excess-3 Code

- 2.5.4 Gray Code

- 2.2.5 Alphanumeric Codes

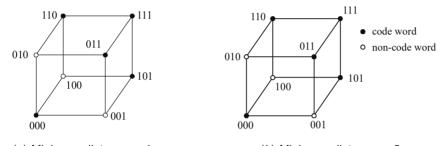

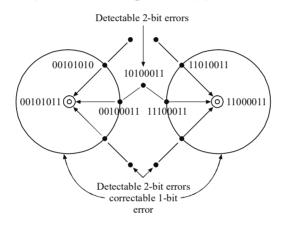

- 2.5.6 Error-Detecting Codes

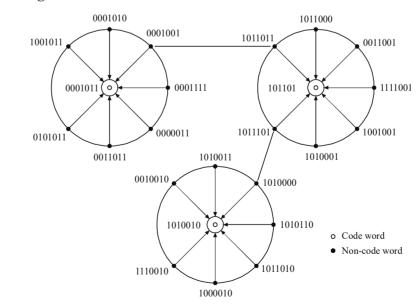

- 2.5.7 Error-Correcting Codes

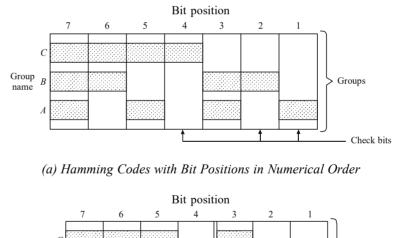

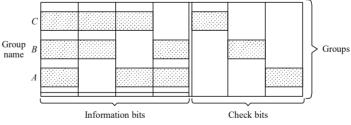

- 2.5.8 Hamming Codes

- 2.6 Computer Instruction

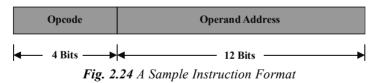

- 2.6.1 Instruction Representation

- 2.7 Timing and Controls

- 2.7.1 Functions of Control Unit

- 2.7.2 Instruction Cycle

- 2.8 Memory Reference Instructions 2.8.1 Memory Reference Format

- 2.9 Input/Output and Interrupts

- 2.10 Complete Computer Description

- 2.10.1 Basic Anatomy of the Computer

- 2.10.2 Data Representation within the Computer

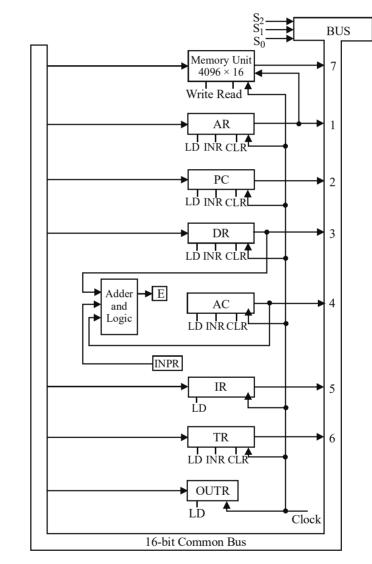

- 2.10.3 Design of a Basic Computer

- 2.10.4 Components of a Computer System

- 2.10.5 Machine Language

- 2.11 Answers to 'Check Your Progress'

- 2.12 Summary

- 2.13 Key Terms

- 2.14 Self-Assessment Questions and Exercises

- 2.15 Further Reading

#### UNIT 3 COMPUTER PROGRAMMING AND MICRO-PROGRAMMING 161-217

- 3.0 Introduction

- 3.1 Objectives

- 3.2 Assembly Language

- 3.2.1 Assembler

- 3.2.2 Program Loops

- 3.2.3 Programming Arithmetic and Logic

- 3.2.4 Subroutines

- 3.2.5 Input/Output Programming

- 3.3 Micro-Programmed Control

- 3.3.1 Address Sequencing

- 3.3.2 Micro-Program Example

- 3.3.3 Design of Control Unit

- 3.4 Answers to 'Check Your Progress'

- 3.5 Summary

- 3.6 Key Terms

- 3.7 Self-Assessment Questions and Exercises

- 3.8 Further Reading

#### UNIT 4 CPU, INPUT-OUTPUT AND MEMORY ORGANIZATIONS 219-342

- 4.0 Introduction

- 4.1 Objectives

- 4.2 Central Processing Unit

- 4.2.1 Fundamental Concepts

- 4.2.2 Organization of Registers in Different Computers

- 4.3 General Register Organization

- 4.3.1 Control Word

- 4.4 Stack Organization

- 4.4.1 Register Stack

- 4.4.2 Memory Stack

- 4.4.3 Reverse Polish Notation

- 4.4.4 Evaluation of Arithmetic Expression

- 4.5 Instruction Formats

- 4.5.1 Addressing Modes

- 4.6 Data Transfer and Manipulation

- 4.6.1 Data Manipulation Instructions

- 4.7 Micro-Programmed Control

- 4.7.1 Execution of Complete Instruction

- 4.7.2 Reduced Instruction Set Computer

- 4.8 Peripheral Device

- 4.8.1 Input-Output Interface

- 4.8.2 Asynchronous Data Transfer

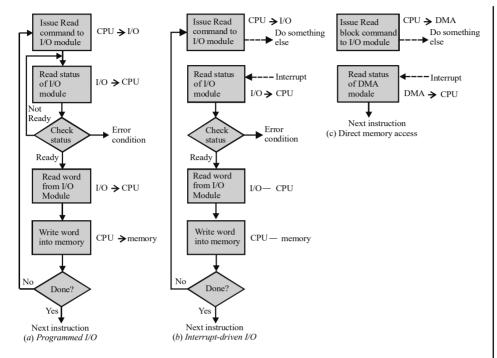

- 4.8.3 Mode of Transfer

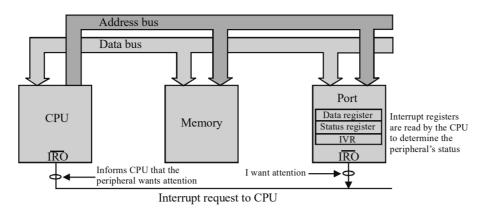

- 4.8.4 Priority Interrupt

- 4.8.5 Direct Memory Access (DMA)

- 4.8.6 Input/Output Processor

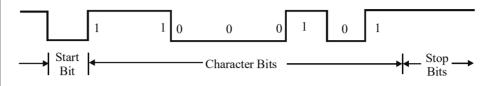

- 4.8.7 Serial Communication

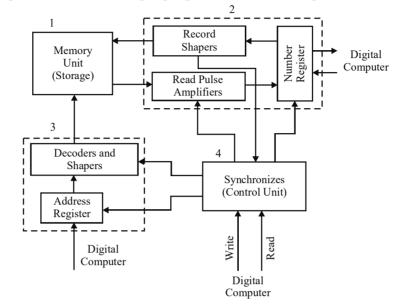

- 4.9 Memory Unit

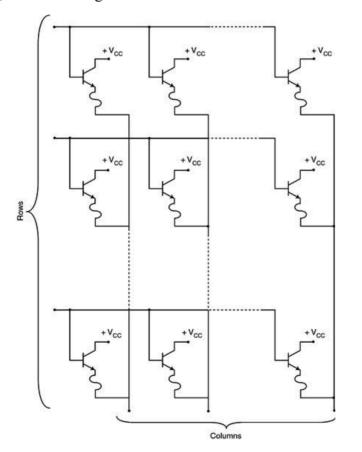

- 4.9.1 Types of Memory

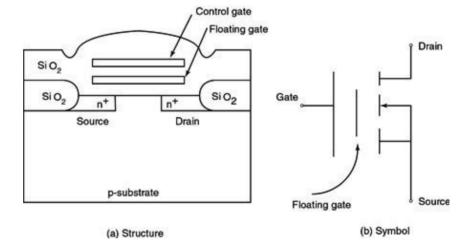

- 4.9.2 Flash Memory

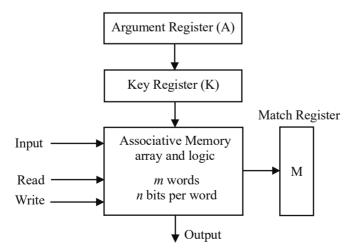

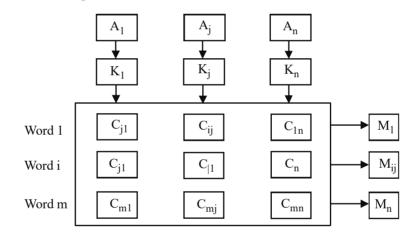

- 4.9.3 Associative Memory

- 4.9.4 Cache Memory

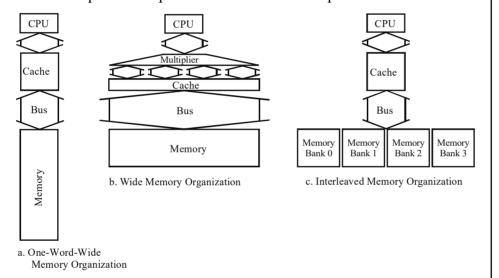

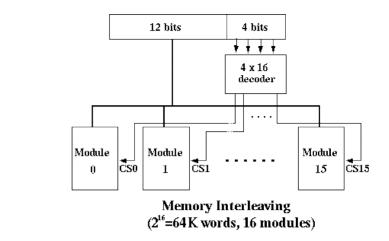

- 4.9.5 Interleaving

- 4.9.6 Hit Rate and Miss Penalty

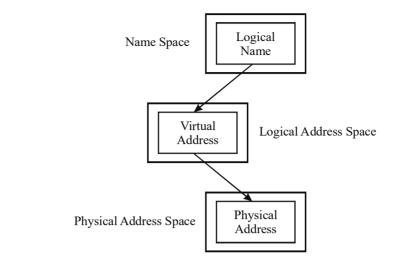

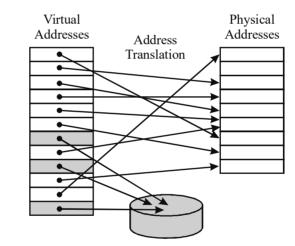

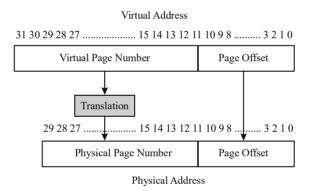

- 4.9.7 Virtual Memory

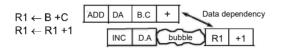

- 4.10 Parallel Processing

- 4.10.1 Overcoming Pipelining Conflicts

- 4.11 Flynn's Classification 4.11.1 Array Processors

- 4.12 Answers to 'Check Your Progress'

- 4.13 Summary

- 4.14 Key Terms

- 4.15 Self-Assessment Questions and Exercises

- 4.16 Further Reading

#### UNIT 5 PIPELINE, VECTOR PROCESSING AND MULTIPROCESSING 343-422

- 5.0 Introduction

- 5.1 Objectives

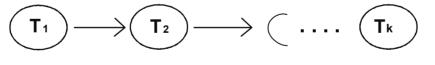

- 5.2 Pipeline Processing

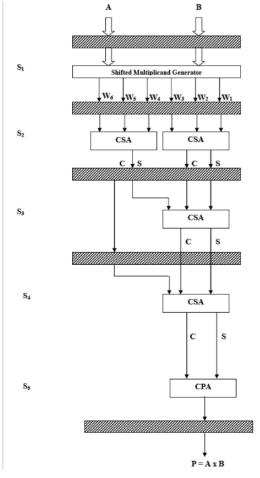

- 5.2.1 Arithmetic Pipeline

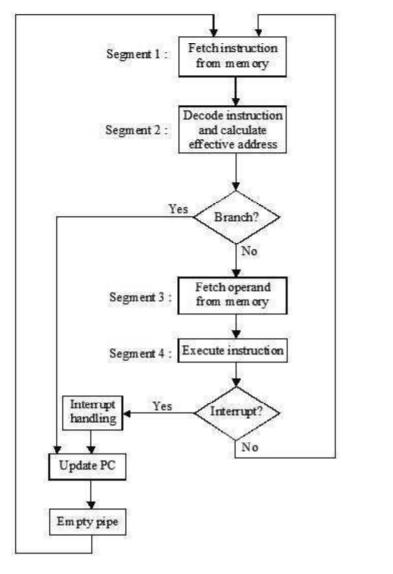

- 5.2.2 Instruction Pipeline

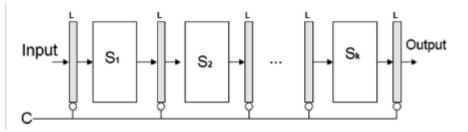

- 5.2.3 Linear Pipeline

- 5.2.4 RISC Pipelines

- 5.2.5 Vector Processing

- 5.2.6 Array Processing

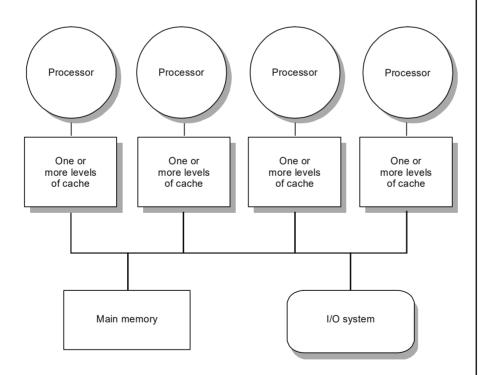

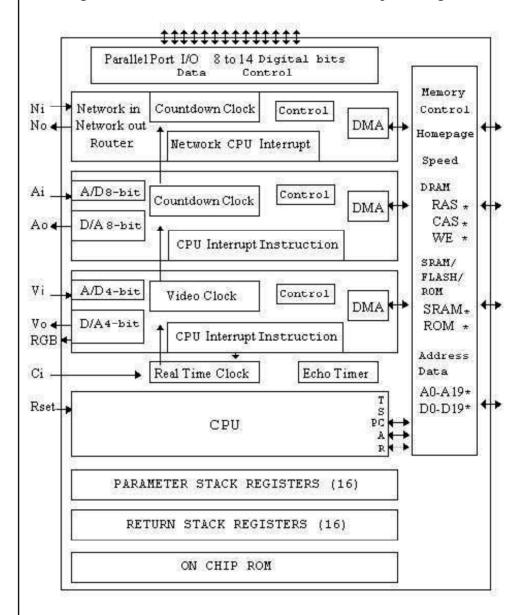

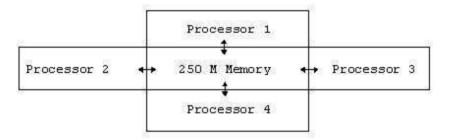

- 5.3 Multiprocessors

- 5.3.1 Interconnection Structure

- 5.3.2 Characteristics of Multiprocessors

- 5.3.3 Interprocess Arbitration

- 5.4 Interprocessor communication and Synchronization

- 5.4.1 Racing Problem

- 5.4.2 Problems of Critical Section

- 5.4.3 Critical Section Algorithms

- 5.4.4 Hardware Support for Mutual Exclusion

- 5.4.5 Swap Instruction

- 5.4.6 Binary Semaphore

- 5.4.7 Implementation of Semaphores with a Waiting Queue

- 5.4.8 Conditional Critical Region (CCR)

- 5.4.9 Classical Problems in Concurrent Programming

- 5.4.10 Readers and Writers Problem

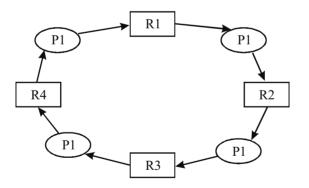

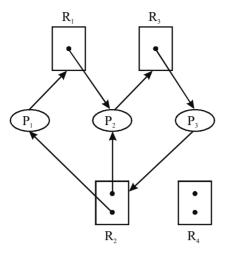

- 5.4.11 Deadlocks

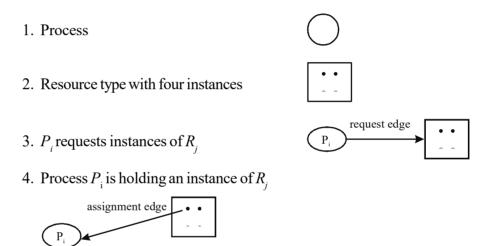

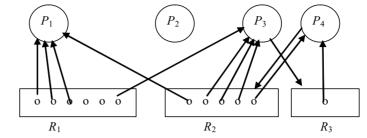

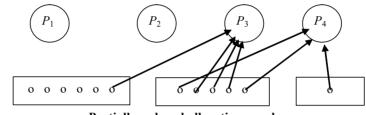

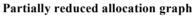

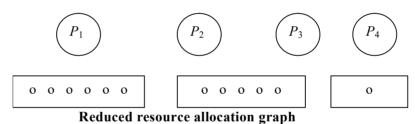

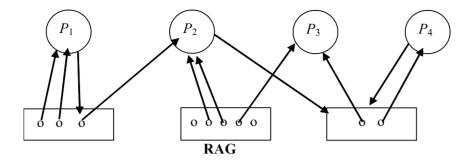

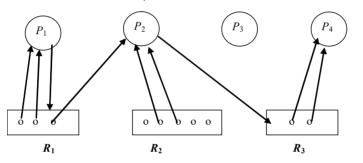

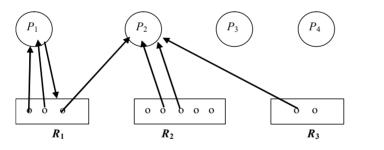

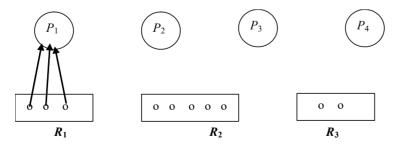

- 5.4.12 Resource Allocation Graph (RAG)

- 5.4.13 Methods for Handling Deadlocks

- 5.4.14 Introduction to File System and IO

- 5.4.15 Organizing Files

- 5.5 Cache Coherence

- 5.6 Answers to 'Check Your Progress'

- 5.7 Summary

- 5.8 Key Terms

- 5.9 Self-Assessment Questions and Exercises

- 5.10 Further Reading

## INTRODUCTION

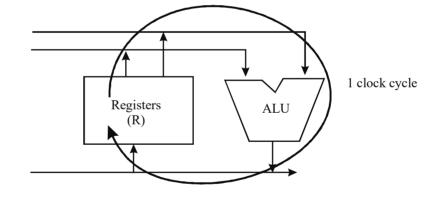

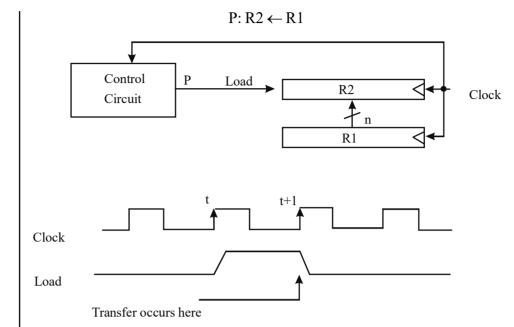

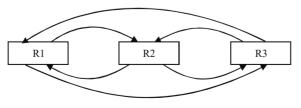

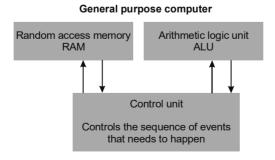

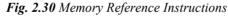

A computer is an electronic device for storing and processing data, typically in binary form, according to instructions given to it in a variable program. In computer engineering, computer architecture is a set of rules and methods that describe the functionality, organization, and implementation of computer systems. The architecture of a system refers to its structure in terms of separately specified components of that system and their interrelationships.

Computer organization helps optimize performance-based products, such as the processing power of processors. Computer organization also helps plan the selection of a processor for a particular project. Multimedia projects may need very rapid data access, while virtual machines may need fast interrupts. Sometimes certain tasks need additional components as well. Computer organization and features also affect power consumption and processor cost.

Fundamentally, the computer architecture involves Instruction Set Architecture (ISA) design, microarchitecture design, logic design, and its implementation.

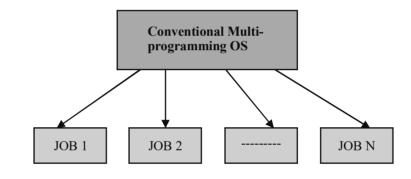

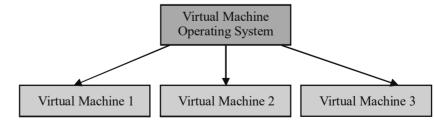

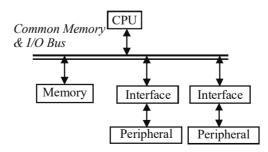

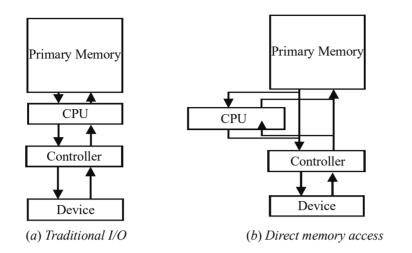

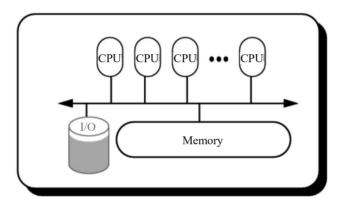

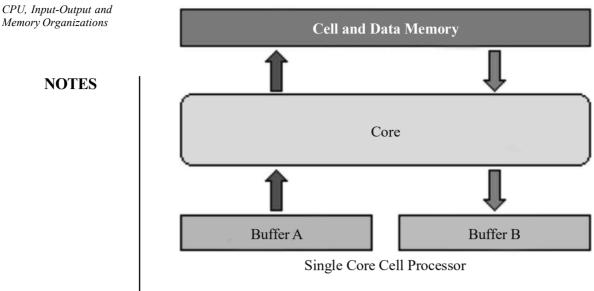

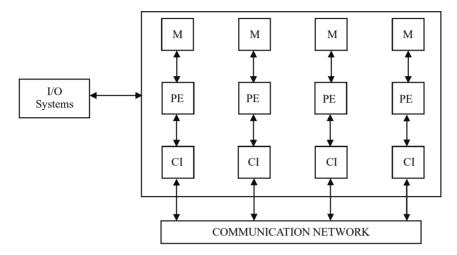

The discipline of computer architecture includes three main subcategories, namely the Instruction Set Architecture (ISA), the microarchitecture and the systems design. The term ISA refers to the machine code that a processor reads and acts upon as well as the word size, memory address modes, processor registers, and data type. Microarchitecture is also known as 'Computer Organization', as it describes how a particular processor will implement the ISA. Systems design includes all of the other hardware components within a computing system, such as data processing other than the CPU, for example Direct Memory Access (DMA), virtualization, and multiprocessing.

Instruction sets have shifted over the years, from initially very simple to sometimes very complex in various respects. A Complex Instruction Set Computer or CISC is a computer where single instructions can execute several low level operations and/or are capable of multi-step operations or addressing modes within single instructions. The term was retroactively coined in contrast to Reduced Instruction Set Computer (RISC). However, the choice of instruction set architecture may greatly affect the complexity of implementing high performance devices. The prominent strategy, used to develop the first RISC processors, was to simplify instructions to a minimum of individual semantic complexity combined with high encoding regularity and simplicity.

This book is divided into five units that attempt to give the students a fair idea of basic computer organization and design, information representation, logic gates, basic building blocks and circuits, computer organization and design concepts, basic computer programming, micro-programming, CPU organization, input-output organization, memory organization, pipeline and vector processing, and multiprocessing The book follows the Self-Instructional Mode or SIM format wherein each unit begins with an 'Introduction' to the topic followed by an outline of the 'Objectives'. The detailed content is then presented in a simple and structured manner interspersed with Answers to 'Check Your Progress' questions. A list of 'Key Terms', a 'Summary' and a set of 'Self-Assessment Questions and Exercises' is also provided at the end of each unit for effective recapitulation.

Introduction

#### NOTES

Self - Learning Material

1

# UNIT 1 INFORMATION REPRESENTATION, LOGIC GATES, BOOLEAN ALGEBRA, CIRCUITS, REGISTERS AND COUNTERS

#### Structure

- 1.0 Introduction

- 1.1 Objectives

- 1.2 Number System

- 1.2.1 Decimal Number System

- 1.2.2 Binary Number System

- 1.3 Floating Point Representation

- 1.3.1 Integer Representation

- 1.3.2 1's Complement Representation

- 1.3.3 2's Complement Representation

- 1.3.4 Complements

- 1.4 Character Codes

- 1.5 Logic Gates

- 1.5.1 NOT Gate

- 1.5.2 AND Gate

- 1.5.3 OR Gate

- 1.5.4 XOR Gate

- 1.6 Boolean Algebra

- 1.6.1 Logical AND Operation

- 1.6.2 Logical OR Operation

- 1.6.3 Logical Complementation (Inversion)

- 1.6.4 Basic Laws of Boolean Algebra

- 1.6.5 De Morgan's Theorems

- 1.6.6 Realization of Expression using Gates

- 1.6.7 Combinational Logic

- 1.7 Boolean Expression Simplification

- 1.7.1 Algebraic Simplification

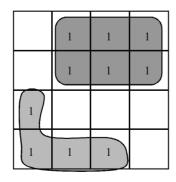

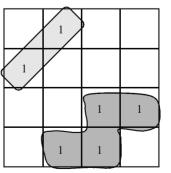

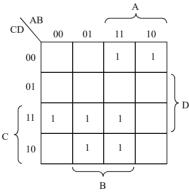

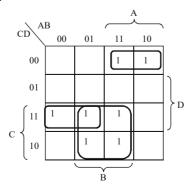

- 1.7.2 Karnaugh Map

- 1.7.3 Steps for Forming Karnaugh Map

- 1.7.4 Simplification of Expressions using Karnaugh Map

- 1.7.5 Simplification using Karnaugh Map

- 1.7.6 Simplest SOP Expressions

- 1.7.7 Getting POS Expressions

- 1.8 Combinational Circuits

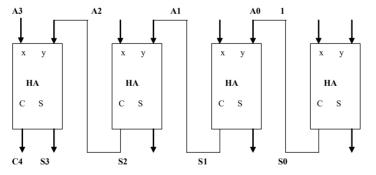

- 1.8.1 Half-Adder

- 1.8.2 Full-Adder

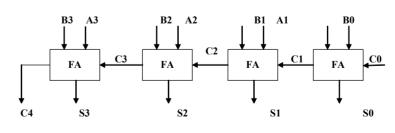

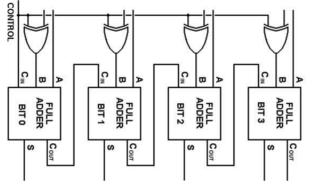

- 1.8.3 Parallel Binary Adder

- 1.8.4 Subtractors

- 1.8.5 Decoders

- 1.8.6 Multiplexer

- 1.8.7 Code Converters

Information Representation, Logic Gates, Bodean Algebra, Circuits, Registers and Carates

NOTES

Self - Learring Material Information Representation, Logic Gates, Boolean Algebra, Circuits, Registers and Counters

NOTES

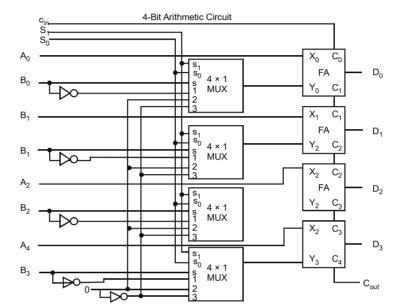

- 1.9 Arithmetic Circuits

- 1.9.1 Binary Addition

- 1.9.2 Binary Subtraction

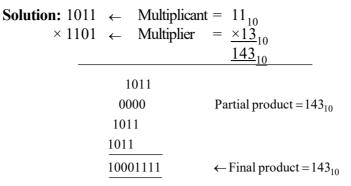

- 1.9.3 Binary Multiplication

- 1.9.4 Binary Division

- 1.10 Combinational Circuits and Sequential Circuits

- 1.10.1 Analysis of a Combinational Circuit

- 1.11 Registers and Counters

- 1.11.1 Serial-In-Serial-Out Shift Registers

- 1.11.2 Serial-In-Parallel-Out Shift Registers

- 1.11.3 Parallel-In-Serial-Out Shift Registers

- 1.11.4 Parallel-In-Parallel-Out Registers

- 1.11.5 Bidirectional Shift Registers

- 1.11.6 Applications of Shift Registers

- 1.12 Answers to 'Check Your Progress'

- 1.13 Summary

- 1.17 Key Terms

- 1.15 Self-Assessment Questions and Exercises

- 1.16 Further Reading

# **1.0 INTRODUCTION**

A number system that uses only two digits, 0 and 1, is called the binary number system. A binary fraction can be represented by a series of 1 and 0 to the right of a binary point. In digital computers, the binary numbers are represented by a set of binary storage devices such as flip flops. A binary number can be converted into decimal number by multiplying the binary 1 or 0 by the weight corresponding to its position and adding all the values.

Floating point representation has a fractional part and is known as the floatingpoint number. Floating point number are those numbers, which include 'Decimals' or 'Fractional Parts' and 'Integer Values'. In integer representation the sign information has to be encoded along with the magnitude to represent the integers completely.

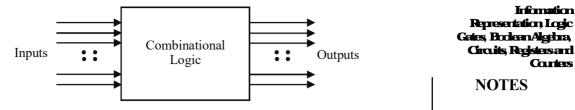

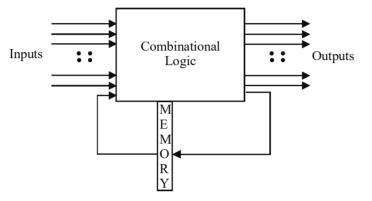

A logic gate is a device that performs Boolean logic on one or more binary inputs before producing a single binary output. Computers often output more than a single binary digit and conduct more than simple Boolean logic operations on supplied data and a combinational circuit is a digital logic circuit in which the output is determined by the combination of inputs at any given time, regardless of the condition of the inputs previously. Combinational circuits are built around the digital logic gate.

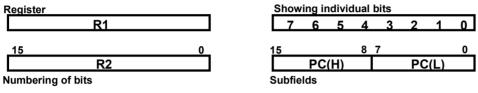

Arithmetic circuits in computers and calculators perform arithmetic and logical operations. All arithmetic operations take place in the arithmetic unit of a computer. A register is a group of flip-flops used to store or manipulated data or both. Each flip-flop is capable of storing one bit of information.

In this unit, you will study about the number system, floating point representation, integer representation, character codes, logic gates, Boolean algebra, Boolean expression simplification, combinational circuits, arithmetic circuits, combinational circuits and sequential circuits, registers and counters.

Self · Learning Material

# **1.1 OBJECTIVES**

After going through this unit, you will be able to:

- Discuss about the different types of number system

- Explain the floating point representation

- Analyse the techniques of integer representation

- Describe the various character codes of computer

- Elaborate on the different types of logic gates

- Discuss about the Boolean algebra

- Describe the simplification techniques of Boolean Expression

- Define combinational circuits

- Understand the significance of the arithmetic circuits

- Differentiate between combinational circuits and sequential circuits

- Explain the term registers

- Discuss the basic features of counters

# **1.2 NUMBER SYSTEM**

A number is an idea that is used to refer amounts of things. People use number words, number gestures and number symbols. Number words are said out loud. Number gestures are made with some part of the body, usually the hands. Number symbols are marked or written down. A number symbol is called a **numeral**. The number is the idea we think of when we see the numeral or when we see or hear the word.

On hearing the word number, we immediately think of the familiar decimal number system with its 10 digits; 0, 1, 2, 3, 4, 5, 6, 7, 8 and 9. These numerals are called **Arabic numerals**. Our present number system provides modern mathematicians and scientists with great advantages over those of previous civilisations, and is an important factor in our advancement. Since fingers are the most convenient tools nature has provided, human beings use them in counting. So the decimal number system followed naturally from this usage.

A number of base, or radix, **r** is a system that uses distinct symbols of **r** digits. Numbers are represented by a string of digit symbols. To determine the quantity that the number represents, it is necessary to multiply each digit by an integer power of **r** and then form the sum of all the weighted digits. It is possible to use any whole number greater than one as a base in building a numeration system. The number of digits used is always equal to the base.

There are four systems of arithmetic, which are often used in digital systems. These systems are: Information Representation, Logic Gates, Boolean Algebra, Circuits, Registens and Counters

NOTES

Self · Learring Material Information Representation Logic Gates, Boolean Algebra, Circuits, Registers and Counters

NOTES

Decimal

Binary

Hexadecimal

4. Octal

In any number system, there is an ordered set of symbols known as **digits**. Collection of these digits makes a number which is general has two parts, integer and fractional, and are set apart by a radix point (.). Hence, a number system can be represented as

$$\mathbf{N}_{\mathbf{b}} = \underbrace{\mathbf{a}_{\mathbf{h}-1}\mathbf{a}_{\mathbf{h}-2}\mathbf{a}_{\mathbf{h}-3}\cdots\mathbf{a}_{\mathbf{a}}}_{\text{Integer portion}} \cdot \underbrace{\mathbf{a}_{1}\mathbf{a}_{2}\mathbf{a}_{3}\cdots\mathbf{a}_{\mathbf{m}}}_{\text{Fractional portion}}$$

where  $\mathbf{N} = a$  number

**b**= radix or base of the number system

**n**= number of digits in integer portion

**m**= number of digits in fractional portion

$\mathbf{a}_{1} = \text{Most Significant Digit (MSD)}$

$\mathbf{a}_{\mathbf{m}} = \text{Least Significant Digit (LSD)}$

and  $0 \leq (\mathbf{a} \text{ or } \mathbf{a}) \leq \mathbf{b}_1$

**Base or Radix:** The base or radix of a number is defined as the number of different digits which can occur in each position in the number system.

# 1.2.1 Decimal Number System

The number system which utilizes ten distinct digits, i.e., 0, 1, 2, 3, 4, 5, 6, 7, 8 and 9 is known as decimal number system. It represents numbers in terms of groups of tens (as shown in Figure 1.1).

We would be forced to stop at 9 or to invent more symbols if it were not for the use of positional notation. It is necessary to learn only 10 basic numbers and positional notational system in order to count any desired figure.

#### Fig. 1.1 Decinal Position Values as Povers of 10

The decimal number system has a base or radix of 10. Each of the ten decimal digits 0 through 9, has a place value or weight depending on its position. The weights are units, tens, hundreds and so on. The same can be written as the power of its base as  $[10^0, 10^1, 10^2, 10^3, ...]$ , etc. Thus, the number 1993 represents quantity equal to 1000 + 900 + 90 + 3. Actually, this should be written as  $\{1 \times 10^3 + 9 \times 10^2 + 9\}$

$\times 10^{1} + 3 \times 10^{0}$ }. Hence, 1993 is the sum of all digits multiplied by their weights.

Self - Learning Material

6

Each position has a value 10 times greater than the position to its right.

**Example 1.1:** The number 379 actually stands for the following representation:

In this example, 9 is the Least Significant Digit (LSD) and 3 is the Most Significant Digit (MSD).

Example 1.2: The number 1936.469 can be written as

Solution:  $1936.469_{10} = 1 \times 10^3 + 9 \times 10^2 + 3 \times 10^1 + 6 \times 10^0 + 4 \times 10^{-1} + 6 \times 10^{-2} + 9 \times 10^{-3}$

= 1000 + 900 + 30 + 6 + 0.4 + 0.06 + 0.009 = 1936.469

It is seen that powers are numbered to the left of the decimal point starting with 0 and to the right of decimal point starting with -1.

The general rule for representing numbers in the decimal system by using positional notation is as follows:

$\mathbf{a}_{\mathbf{n}_{-1}} \cdots \mathbf{a}_{2} \mathbf{a}_{1} \mathbf{a}_{0} = \mathbf{a}_{1}^{10} \mathbf{n}_{+} \mathbf{a}_{\mathbf{n}_{-1}} \mathbf{10}^{\mathbf{n}_{-1}} + \cdots \mathbf{a}_{2}^{10^{2}} + \mathbf{a}_{1}^{10^{1}} + \mathbf{a}_{1}^{10^{0}}$

where **m** is the number of digits to the left of the decimal point.

#### **1.2.2 Binary Number System**

A number system that uses only two digits, 0 and 1 is called the **binary number system**. The binary number system is also called a **base two system**. The two symbols 0 and 1 are known as **bits** (binary digits).

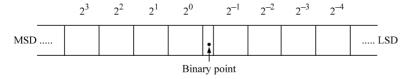

The binary system groups numbers by two's and by powers of two (as shown in Figure 1.2). The word binary comes from a Latin word meaning two at a time.

Fig. 1.2 BinaryPositionValues as a Pover of 2

The weight or place value of each position can be expressed in terms of 2, and as  $2^0$ ,  $2^1$ ,  $2^2$ , etc. The least significant digit has a weight of  $2^0$  (= 1). The second position to the left of the least significant digit is multiplied by  $2^1$  (=2). The third position has weight equal to  $2^2$  (=4). Thus, the weights are in the ascending powers of 2 or 1, 2, 4, 8, 16, 32, 64, 128, etc.

The numeral  $10_2$  (one, zero, base two) stands for two, the base of the system.

In bianry counting, single digits are used for none and one. Two-digit numbers are used for 10, and 11, [2 and 3 in decimal numerals]. For the next counting

Self · Learring Material

7

Information Representation, Logic Gates, Boclean Algebra, Circuits, Registers and Carates

NOTES

Information Representation, Logic Gales, Boolean Algebra, Circuits, Registers and Counters

NOTES

number,  $100_2$  (4 in decimal numerals) three digits are necessary. After  $111_2$  (7 in decimal numerals) four digit numerals are used until  $1111_2$  (15 in decimal numerals) is reached, and so on. In a binary numeral every position has a value 2 times the value of the position to its right.

A binary number with 4 bits, is called a **nibble** and binary number with 8 bits is known as a byte.

**Example 1.3:** The number  $1011_2$  actually stands for the following representation: Solution:  $1011_2 = 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 1 \times 2^0$

$1011_2 = 8 + 0 + 2 + 1 = 11_{10}$

$= 1 \times 8 + 0 \times 4 + 1 \times 2 + 1 \times 1$

In general,

ċ.

$$[\mathbf{b}_{\mathbf{h}}\mathbf{b}_{\mathbf{h}-1}\cdots\mathbf{b}_{2},\mathbf{b}_{1},\mathbf{b}_{2}]_{2} = \mathbf{b}_{\mathbf{h}}^{2\mathbf{n}} + \mathbf{b}_{\mathbf{h}-1}^{2\mathbf{n}} 2^{\mathbf{n}} + \dots + \mathbf{b}_{2}^{2^{2}} + \mathbf{b}_{1}^{2^{1}} + \mathbf{b}_{2}^{2^{0}}$$

Example 1.4: The binary number 10101.011 can be written as

| Solution: |      | 1              | 0              | 1              | 0              | 1              |                | 0            | 1                | 1                                   |

|-----------|------|----------------|----------------|----------------|----------------|----------------|----------------|--------------|------------------|-------------------------------------|

|           |      | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> |                | $2^{-1}$     | $2^{-2}$         | $2^{-3}$                            |

|           |      | (MSI           | D)             |                |                |                |                | (LSD         | ))               |                                     |

|           | 1010 | 01.01          | $l_2 = 1$      | $\times 2^4$   | $+0 \times$    | $2^3 + 2^3$    | $1 \times 2^2$ | $+0 \times$  | 2 <sup>1</sup> + | $1 \times 2^0$                      |

|           |      |                |                |                |                |                | +              | $0 \times 2$ | -1 + 1           | $1 \times 2^{-2} + 1 \times 2^{-3}$ |

|           |      |                | = 1            | 6 + 0          | +4+            | 0 + 1          | + 0 +          | - 0.25       | +0.1             | 25 = <b>21.375</b> <sub>10</sub>    |

In each binary digit, the value increases in powers of two starting with 0 to the left of the binary point and decreases to the right of the binary point starting with power -1.

#### Why Binary Number System is Used

Binary number system is used in digital computers because all electrical and electronic circuits can be made to respond to the two states concept. For instance: a switch can be either opened or closed, only two possible states exist. A transistor can be made to operate either in cut-off or saturation; a magnetic tape can be either magnetised or non-magnetised; a signal can be either HIGH or LOW; a punched tape can have a hole or no hole. In all of the above illustrations, each device is operated in any one of the two possible states and the intermediate condition does not exist. Thus, 0 can represent one of the states and 1 can represent the other. Hence, binary numbers are convenient to use in analysing or designing digital circuits.

#### **Binary Fraction**

A binary fraction can be represented by a series of 1 and 0 to the right of a binary point. The weights of digit positions to the right of the binary point are given by  $2^{-1}$ ,  $2^{-2}$ ,  $2^{-3}$  and so on.

Example 1.5: The binary fraction 0.1011 can be written as Solution:  $0.1011 = 1 \times 2^{-1} + 0 \times 2^{-2} + 1 \times 2^{-3} + 1 \times 2^{-4}$  $= 1 \times 0.5 + 0 \times 0.25 + 1 \times 0.125 + 1 \times 0.0625$  $0.1011_2 = 0.6875_{10}$

Self - Learring Material

8

#### **Mixed Numbers**

Mixed numbers contain both integer and fractional parts. The weights of mixed numbers are

$$2^3$$

$2^2$   $2^1$  .  $2^{-1}$   $2^{-2}$   $2^{-3}$  etc.

**Binary Point**

Example 1.6: A mixed binary numbers 1011.101 can be written as Solution:  $1011.101_2 = 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 1 \times 2^0 + 1 \times 2^{-1} + 0 \times 2^{-2} + 1 \times 2^{-3}$  $= 1 \times 8 + 0 \times 4 + 1 \times 2 + 1 \times 1 + 1 \times 0.5 + 0 \times 0.25 + 1 \times 0.125$

$\therefore$  [1011.101]<sub>2</sub> = [11.625]<sub>10</sub>

When different number systems are used, it is customary to enclose the number within big brackets and the subscripts indicate the type of the number system.

# **1.3 FLOATING POINT REPRESENTATION**

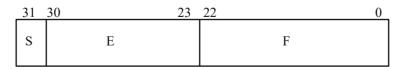

In floating point representation integers can be represented on a computer. However, there is another type of number, which has a fractional part and is known as the floating-point number. Floating-point numbers are those numbers, which include 'Decimals' or 'Fractional Parts' and 'Integer Values', for example, representation of decimal 5.25 can be given as 101.01 in binary. The problem is how to show the decimal point since you are limited to using only 0 or 1 in a binary system. The most widely used presentation is the IEEE 754 floating-point presentation, which presents standards for both 32-bit and 64-bit floating-point numbers.

According to the IEEE standard, the leftmost bit represents the sign of the number. Sign bit 0 is used for the positive sign and 1 for the negative sign. Then the rest is divided into two parts, namely, exponent and mantissa. Since this presentation does not want to 'Waste' a sign bit for the exponent, it decides to use the lower half of the exponential value as negative and the upper half as positive. This will become clearer later with examples.

The 32-bit presentation in the IEEE floating-point standard will be as follows:

Here S = Sign bit, in the leftmost position; S = 1 for -ve number and 0 for +ve number.

E = The 'Exponent' in the next 8-bits.

F = The normalized fractional part in the last 23-bits.

Information Representation, Logic Gales, BodeanAlgebra, Circuits, Registers and Counters

#### NOTES

Self - Learning Material Information Representation, Logic Gales, Bodean Algebra, Circuits, Registers and Counters

NOTES

For converting the above to a decimal value, we have to use the following formula:

$$V = (-1)^{s} \times 2^{E-127} \times 1.F$$

It is to be noted that there is 127 in the exponent term. Why? Since E is

made up of 8-bits, it ranges from 0000000 = 0 to 11111111 = 255 and  $\frac{1}{2}$  of 255 is 127.5 or simply 127. In this way, E = 127 will give the exponent 0; anything above 127 will result in a positive exponent and anything below 127 will result in a negative exponent. The above is known as **excess 127** presentations.

$V = (-1)^{0} \times 2^{128-127} \times 1.5 = 1 \times 2^{1} \times 1.5 = 3.0$

1

For example,

Represent - 2.5 in the IEEE754 32-bit floating-point standard.

Since its negative number, S = 1. Then convert 2.5 to binary, which comes out to be 10.1. Normalize this to  $1.01 \times 2^1$ . To fit this into V =  $(-1)^8 \times 2^{E-127} \times 1.F$ , E = 128 and F = 01000...0. Therefore, the representation of -2.5 is,

1000000

For example,

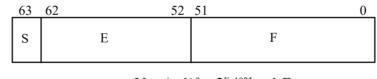

The IEEE standard for 64-bit floating-point representation is similar to the 32-bit standard. The format is shown along with its conversion formula.

$V = (-1)^{S} \times 2^{E-1023} \times 1.F$

Since the integer value 1 is assumed to be invisibly stored with each number in both the 32- and 64-bit representations, you may wonder how the number 0.0 can be represented.

For this, there is an exception. Whenever **both** E and F are **all** 0s, V = 0.0.

How do you add or subtract floating-point values? Obviously, the adders you have learned earlier will not work here. This is similar to when you add or subtract numbers with decimal points where you have to first line up the decimals. Likewise, to add or subtract floating-point numbers, you will have to first modify the F of one of the two numbers by shifting left or right to make it equal to the E of the other number. Then and only then can you add the two F's.

## **1.3.1** Integer Representation

The integers that were discussed so far are unsigned integers; signed integers have been ignored till now. However, the problem with signed integers is how to present a sign. The sign information has to be encoded along with the magnitude to represent the integers completely. The following are the three possible techniques for representing signed integers:

- Signed Magnitude Representation

- Diminished Radix-Complement Representation

- Radix-Complement Representation

#### **Signed Magnitude Representation**

In the Signed Magnitude (SM) representation, the Most Significant Bit (MSB) is used to represent the sign as follows:

'1' is used for a '-' (Negative Sign)

'0' is used for a '+' (Positive Sign)

#### Format of SM Representation

SM number in 8-bits looks like smmmmmmm, where 's' at the MSB location represents sign and the other 7-bits represent the magnitude.

*Note:* For positive numbers, this presentation is the same as the unsigned binary representation for any number.

#### Signed Magnitude Examples (8-Bits)

The following examples show the SM (Signed Magnitude) representation and their corresponding hex numbers:

$$-5 = (10000101)_{2} = (85)_{16}$$

+5 = (00000101)\_{2} = (05)\_{16}

+127 = (0111111)\_{2} = (7F)\_{16}

-127 = (1111111)\_{2} = (FF)\_{16}

+ 0 = (00000000)\_{2} = (00)\_{16}

- 0 = (10000000)\_{2} = (80)\_{16}

With N-bits, you can represent the signed integers that range from,

$-\{2^{(N-1)}-1\} \ to \ \{2^{(N-1)}-1\}.$

For example, with 8-bits, you can represent the signed integers ranging from -127 to +127. Signed magnitude is easy to understand and can be encoded easily and hence, finds its application in digital electronics.

Information Representation, Logic Gates, BooleanAlgebra, Circuits, Registers and Counters

#### NOTES

Self · Learning Material Information Representation, Logic Gates, Boolean Algebra, Circuits, Registers and Counters

NOTES

#### **Problems with Signed Magnitude Representation**

One problem with signed magnitude representation is that it has two ways of representing 0(-0 and + 0). Another problem is that addition of N + (-N) does not give result as zero. For example,

$$-5+5=(85)_{16}+(05)_{16}=(8A)_{16}=-10$$

In order to remove this ambiguity, new representations are proposed. They are one's complement (1's) representation and two's complement (2's) representation for signed integers. These complements are used to represent only the signed integers and for the positive numbers, this representation is same as that of simple binary representation.

# **1.3.2** 1's Complement Representation

1's complement is another way to represent signed integers. In this presentation, for the case of a negative number, first get the binary representation of its magnitude, and then complement each bit, i.e., replace 1 with 0 and vice versa.

**Example 1.7** Represent – 5 in 1's complement in 8-bits.

Solution:

Step 1: First, find the magnitude 5 in 8-bits.

$(00000101)_{2} = (05)_{16}$

Step 2: Then complement each bit as per rule.

$(11111010)_{2} = (FA)_{16}$

Hence,  $(FA)_{16}$  is the 8-bit one's complement representation of -5.

#### Examples

The following examples show 1's complement representation and their corresponding hex for some numbers:

$-5 = (11111010)_{2} = (FA)_{16}$ + 5 = (00000101)\_{2} = (05)\_{16} + 127 = (0111111)\_{2} = (7F)\_{16} - 127 = (10000000)\_{2} = (80)\_{16} + 0 = (00000000)\_{2} = (00)\_{16} - 0 = (1111111)\_{2} = (FF)\_{16}

In N-bits representation, you can represent the signed integers ranging from  $-\{2^{(N-1)}-1\}$  to  $\{2^{(N-1)}-1\}$ . In 8-bits, you can represent the signed integers from -127 to +127. However, the above representation has a problem in presenting 0, since there will be two ways of representing 0 like -0 and +0. However, addition of N + (-N) now gives the result as zero.

$$-5+5 = (FA)_{16} + (05)_{16}$$

=  $(FF)_{16} = -0$

Some more observations for using 1's complement are given as follows:

Self - Learning 12 Material For example, K + 0 = K will work if you use + 0 and it will not satisfy the result if you use -0, in place of 0.

$$5 + (+ 0) = (05)_{16} + (00)_{16} = (05)_{16} = 5$$

(Correct)

$5 + (-0) = (05)_{16} + (FF)_{16} = (04)_{16} = 4$  (Wrong)

So, the two's complement representation comes into the picture.

# 1.3.3 2's Complement Representation

2's complement is used to represent signed integers, especially negative integers. Whenever you need to encode a negative number, first get the binary representation of its magnitude, complement each bit and then add 1. For example, 2's complement of -5 in 8-bits can be obtained as follows:

Step 1: The magnitude 5 in 8-bits

$$(00000101)_{2} = (05)_{16}$$

Step 2: Taking complement of each bit

$$(11111010)_{2} = (FA)_{1}$$

Step 3: Adding one will result 2's complement

$$11111011 = (FA)_{16} + 1 = (FB)_{16}$$

So,  $(11111011)_2$  in binary and  $(FB)_{16}$  in Hex is the 8-bit two's complement representation of -5.

The following examples show 2's complement representation and their corresponding Hex number.

$$-5 = (11111011) = (FB)_{16}$$

+ 5 = (00000101) = (05)\_{16}

+ 127 = (01111111) = (7F)\_{16}

- 127 = (10000001) = (81)\_{16}

- 128 = (10000000) = (80)\_{16}

+ 0 = (00000000) = (00)\_{16}

- 0 = (00000000) = (00)\_{16}

In N-bits, you can represent the signed integers ranging from  $-2^{(N-1)}$  to  $2^{(N-1)} - 1$ . It is to be noted that the negative range extends one more than the positive range. For example, in 8-bits, you can represent the signed integers from -128 to +127.

It is to be noted that the 2's complement representation of any signed number has none of the drawbacks like the signed magnitude or one's complement representation, since there is only one representation for zero, i.e., for +0 and -0, and N + (-N) = 0.

For example,  $-5 + 5 = (FB)_{16} + (05)_{16} = (00)_{16} = 0$

#### **1.3.4** Complements

Complements are used in digital computers for simplifying the subtraction operation and for logic manipulations. There are two types of complements for each base R system, which are as follows:

Self · Learning Material

13

Information Representation, Logic Gates, Boolean Algebra, Circuits, Registers and Carnets

NOTES

Information Representation Logic Gates, Boolean Algebra, Circuits, Registers and Counters

NOTES

- Diminished Radix-Complement Representation [(R-1)'s Complement]

- Radix-Complement Representation [R's Complement]

#### (R - 1)'s Complement Representation

For positive numbers, you need to represent by sign and magnitude and for negative numbers – N, you need to represent it by  $\tilde{N}$ , the (R – 1)'s complement where,

$$\tilde{\mathbf{N}} = (\mathbf{R}^{n} - \mathbf{R}^{-m}) - \mathbf{N}$$

$\mathbf{n}$  = Total number of digits in integer part of the number N

$\mathbf{m}$  = Total number of digits in fractional part of the number N

For example,

9's complements of  $(52520)_{10} = (10^5 - 10^0 - 52520) = (10^5 - 1 - 52520) = 47479$ 9's complements of  $(0.3267)_{10} = (10^0 - 10^{-4} - 0.3267) = (0.9999 - 0.3267) =$

0.6732

#### **R's Complement Representation**

For positive numbers, you need to represent by sign and magnitude and for negative numbers – N, you need to represent it by  $\tilde{N}$ , the (R)'s complement where

$$\tilde{N} = R^n - N$$

$\mathbf{n}$  = Total number of digits in the integer part of the number N

For example,

10's complements of  $(52520)_{10} = (10^5 - 52520) = 47480$

10's complements of  $(0.3267)_{10} = (10^0 - 0.3267) = (1.0 - 0.3267) = 0.6733$

# **1.4 CHARACTER CODES**

Most of the processing in computers and other digital circuits are done in the binary formats. Various binary codes are used to represent data, which may be numerals, alphabets or special characters. A user must be very careful about the code being used while interpreting information available in the binary format. For example,

1000001 represents  $(65)_{10}$  in straight binary.

1000001 represents  $(41)_{10}$  in BCD.

1000001 represents A in ASCII code.

Some commonly used codes are as follows:

- Straight Binary Codes

- Natural BCD Codes

- Excess-3 Codes

- Gray Codes

- Alphanumeric Codes

Self - Learning 14 Material

• Error Codes

#### 1. Straight Binary Codes

One binary digit (one bit) can take on values 0 and 1. This is used to represent numbers using a natural (straight) binary form as discussed earlier. For example,  $(65)_{10}$  in straight binary is represented by 1000001. Examples of other binary representations are: {Black = 0, White = 1}, {True = 1, False = 0}, {On = 1, Off = 0}.

Similarly, two binary digits (two bits) can represent four different values like 00, 01, 10 and 11.

In general, N-bits (or N binary digits) can represent 2<sup>N</sup> different values.

For example, 4-bits can represent  $2^4$  or 16 different values. N-bits can take on unsigned decimal values from 0 to  $2^N - 1$ .

#### 2. Natural BCD Codes

BCD stands for Binary Coded Decimal. In BCD codes, decimal digits 0 through 9 are represented by their natural binary equivalents using four bits, and each decimal digit of a decimal number is represented by this four bits code individually. It is also known as 8, 4, 2, 1 codes where 8, 4, 2, 1 are the weights of the four bits of the decimal digits similar to the straight binary number system. The given Table 1.1 shows the BCD representation for the decimal number:

| Decimal<br>Number | BCD Codes |

|-------------------|-----------|

| 0                 | 0000      |

| 1                 | 0001      |

| 2                 | 0010      |

| 3                 | 0011      |

| 4                 | 0100      |

| 5                 | 0101      |

| 6                 | 0110      |

| 7                 | 0111      |

| 8                 | 1000      |

| 9                 | 1001      |

Table 1.1 BCD Representation for Decinal Number

From the table, it is clear that BCD codes are only valid for decimal numbers less than 10. So, if the need arises to represent a decimal value greater than 9 in the BCD format, then each digit in the decimal number is to be represented individually by the corresponding BCD code.

For example,

$(23)_{10}$  is represented by 0010 0011 in BCD

$(08)_{10}$  is represented by 0000 1000 in BCD

$(921)_{10}$  is represented by 1001 0010 0001 in BCD

Similarly, if you have a BCD number presentation and you have to find its equivalent integer value, then you have to make a group of 4-bits starting from the LSB bit to the MSB bit. If the last group does not have 4-bits, then pad with zeros.

Self · Learring Material

Information Representation, Logic Gates, Boolean Algebra, Circuits, Registers and Cantas

NOTES

Information Representation, Logic Gates, Bodean Algebra, Circuits, Registers and Counters

NOTES

For example,

01010010 represents 52<sub>10</sub> 01110011 represents 73<sub>10</sub>

#### 3. Excess-3 Codes

This is another form of BCD code in which each decimal digit is coded into a 4-bit binary code. The code for each decimal digit is obtained by adding decimal 3 to the corresponding BCD code. For example, decimal 2 is coded as 0010 + 0011 = 0101 in the excess-3 code.

It is not a weighted code like straight binary or BCD code. Also, it is a selfcomplementing code, which means that 1's complement of the coded number yields 9's complement of the number itself. For example, the excess-3 code of decimal 2 is 0101 and its 1's complement is 1010, which is excess-3 code for decimal 7. It also represents the 9's complement of 2.

This property helps in performing subtraction operation in digital systems. The complete Table 1.2 is as follows:

| Decimal<br>Number | BCD<br>Codes | Excess-3<br>Code |

|-------------------|--------------|------------------|

| 0                 | 0000         | 0011             |

| 1                 | 0001         | 0100             |

| 2                 | 0010         | 0101             |

| 3                 | 0011         | 0110             |

| 4                 | 0100         | 0111             |

| 5                 | 0101         | 1000             |

| 6                 | 0110         | 1001             |

| 7                 | 0111         | 1010             |

| 8                 | 1000         | 1011             |

| 9                 | 1001         | 1100             |

#### Table 1.2 Excess 3Codes

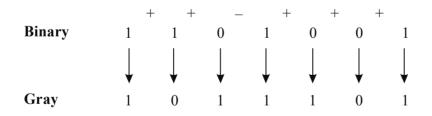

#### 4. Gray Codes

It is a very useful code in which a decimal number is represented in the binary form in such a way that each Gray code differs from the preceding and the succeeding numbers by a single bit. It is not a weighted code. It is also known as reflected code.

#### **Construction of Gray Code**

A 1-bit Gray code has two codes 0 and 1 representing decimal numbers 0 and 1. An n-bit (n>=2) Gray code will have first  $2^{n-1}$  Gray codes with n-1 bits (Least Significant Bits or LSB) written in order with a leading 0 appended; and the last  $2^{n-1}$  Gray codes with n-1 bits (LSB) written in the reverse order (mirror image) with a leading 1 appended.

| For example,    |   |          |    |

|-----------------|---|----------|----|

| 1-Bit Gray Code |   |          |    |

| Decimal Number  | G | iray Coc | le |

| 0               |   | 0        |    |

| 1               |   | 1        |    |

| 2-Bit Gray Code |   |          |    |

| Decimal Number  | G | ray Coc  | le |

| 0               |   | 00       |    |

| 1               |   | 01       |    |

| 2               |   | 11       |    |

| 3               |   | 10       |    |

| 3-Bit Gray Code |   |          |    |

| Decimal Number  | G | ray Coc  | le |

| 0               | 0 | 0        | 0  |

| 1               | 0 | 0        | 1  |

| 2               | 0 | 1        | 1  |

| 3               | 0 | 1        | 0  |

| 4               | 1 | 1        | 0  |

| 5               | 1 | 1        | 1  |

| 6               | 1 | 0        | 1  |

| 7               | 1 | 0        | 0  |

Information Representation, Logic Gales, Bodean Algebra, Circuits, Registers and Carriers

#### NOTES

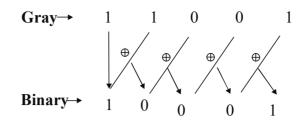

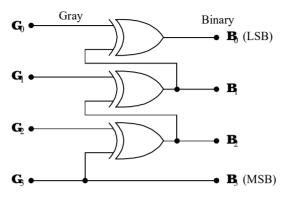

#### **Conversion from Binary to Gray**

The MSB of Gray code is the same as the MSB of the corresponding binary code. EXOR is the MSB to the next bit of the binary number. This will give the next bit of the Gray code number. Continue the EXOR operation on each bit of the binary to the next bit to its right to get the Gray code for that position shown as follows:

#### **Conversion from Gray to Binary**

The MSB of binary code is the same as the MSB of the corresponding Gray code. EXOR is the result of the binary code to the next bit of the Gray code number to get the next bit of the binary code number. Continue the EXOR operation on the result bit of the binary code to the next bit of the Gray code to get the binary code for that position as follows:

Self · Learning Material Information Representation, Logic Gates, Boolean Algebra, Circuits, Registers and Counters

NOTES

#### 5. Alphanumeric Codes

Sometimes, digital systems are required to handle data that may consist of numerals, letters and special symbols. If you use an n-bit binary code, you can represent 2<sup>n</sup> elements using this code. Therefore, to represent 10 digits 0 through 9 and 26 alphabets A through Z, you need a minimum of 6-bits.

In some applications, sometimes it is required to represent more than 64 characters including the lower-case letters and the special control characters for the transmission of the digital information. For this reason, make use of the new codes, namely:

- Extended BCD Interchange Code (EBCDIC)

- American Standard Code for Information Interchange (ASCII)

#### American Standard Code for Information Interchange (ASCII)

This is required for representing more than 64 characters. It is a 7-bit code, so a maximum of 128 different characters can be represented by this code. For example, 1000001 is the ASCII representation of alphabet A.

#### **Extended BCD Interchange Code (EBCDIC)**

It is also used to represent more than 64 characters and it is an 8-bit code. The 8bit (Most Significant Bit or MSB) is invariably added for parity. A maximum of 128 different characters can be represented by this code. A parity bit is an extra bit included with the message to make the total number of 1's either odd or even, depending on the parity need either even or odd. Odd parity makes the total number of 1's odd including parity bit and even parity makes the total number of 1's even, including parity bit. For example, 11000001 is the EBCDIC representation of alphabet A.

The table for the EBCDIC is as follows:

| Character | 6-bit<br>Internal Code | 8-bit<br>EBCDIC |

|-----------|------------------------|-----------------|

| А         | 010001                 | 11000001        |

| В         | 010010                 | 11000010        |

| С         | 010011                 | 11000011        |

| D         | 010100                 | 11000100        |

| Е         | 010101                 | 11000111        |

| F         | 010110                 | 11000110        |

| Н         | 011000                 | 11001000        |

| Ι         | 011001                 | 11001001        |

Self - Learning 18 Material

| J     | 100001 | 11010001 |

|-------|--------|----------|

| Κ     | 100010 | 11010010 |

| L     | 100011 | 11010011 |

| М     | 100100 | 11010100 |

| Ν     | 100101 | 11010101 |

| 0     | 100110 | 11010110 |

| Р     | 100111 | 11010111 |

| Q     | 101000 | 11011000 |

| R     | 101001 | 11011001 |

| S     | 110010 | 11100010 |

| Т     | 110011 | 11100011 |

| U     | 110100 | 11100100 |

| V     | 110101 | 11100101 |

| W     | 110110 | 11100110 |

| Х     | 110111 | 11100111 |

| Y     | 111000 | 11101000 |

| Ζ     | 111001 | 11101001 |

| 0     | 000000 | 11110000 |

| 1     | 000001 | 11110001 |

| 2     | 000010 | 11110010 |

| 3     | 000011 | 11110011 |

| 4     | 000100 | 11110100 |

| 5     | 000101 | 11110101 |

| 6     | 000110 | 11110110 |

| 7     | 000111 | 11110111 |

| 8     | 001000 | 11111000 |

| 9     | 001001 | 11111001 |

| blank | 110000 | 01000000 |

| O     | 011011 | 01001011 |

| (     | 111100 | 01001101 |

| +     | 010000 | 01001110 |

| \$    | 101011 | 01011011 |

| *     | 101100 | 01011100 |

| ,     | 011100 | 01011101 |

| _     | 100000 | 01100000 |

| 1     | 110001 | 01101011 |

| ,     | 111011 | 01101011 |

| =     | 001011 | 01111110 |

|       |        |          |

# **Check Your Progress**

- 1. What is binary number system?

- 2. Define mixed numbers.

3. How do you add or subtract floating-point values?

- 4. What are the three possible techniques for representing signed integers?

- 5. State the character codes of computers.

Self · Learning Material

Information

Canters

Representation, Logic Gates, BockeanAlgebra, Circuits, Registers and

NOTES

Information Representation, Logic Gates, BockennAlgebra, Circuits, Registers and Counters

NOTES

# **1.5 LOGIC GATES**

A logic gate is an idealized model of computation or physical electronic device implementing a Boolean function, a logical operation performed on one or more binary inputs that produces a single binary output. Depending on the context, the term may refer to an ideal logic gate, one that has for instance zero rise time and unlimited fan-out, or it may refer to a non-ideal physical device.

Logic gates are primarily implemented using diodes or transistors acting as electronic switches, but can also be constructed using vacuum tubes, electromagnetic relays (relay logic), fluidic logic, pneumatic logic, optics, molecules, or even mechanical elements. With amplification, logic gates can be cascaded in the same way that Boolean functions can be composed, allowing the construction of a physical model of all of Boolean logic, and therefore, all of the algorithms and mathematics that can be described with Boolean logic.

Logic circuits include such devices as multiplexers, registers, Arithmetic Logic Units (ALUs), and computer memory, all the way up through complete microprocessors, which may contain more than 100 million gates. In modern practice, most gates are made from MOSFETs (Metal–Oxide–Semiconductor Field-Effect Transistors).

Compound logic gates AND-OR-Invert (AOI) and OR-AND-Invert (OAI) are often employed in circuit design because their construction using MOSFETs is simpler and more efficient than the sum of the individual gates.

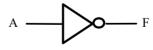

# 1.5.1 NOT Gate

The basic NOT gate has only one input and one output. The output is always the opposite or negation of the input. The following is the truth table for NOT gate:

| Table 1.3 ' | Tiuth Table for NOT Gate |

|-------------|--------------------------|

|-------------|--------------------------|

| Α | F |

|---|---|

| 0 | 1 |

| 1 | 0 |

#### Symbol: F = A'

The following is the figure of NOT gate representation:

Fig. 1.3 NOTGate

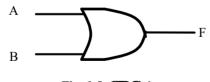

# 1.5.2 AND Gate

A basic AND gate consists of two inputs and an output. In the AND gate, the output is '**High**' or gate is '**On**' only if both the inputs are '**High**'. The relationship between the input signals and the output signals is often represented in the form of a **truth table**. It is nothing but a tabulation of all possible input combinations and the resulting outputs. For the AND gate, there are four possible combinations of

input states:  $\{\mathbf{A}=0, \mathbf{B}=0\}$ ;  $\{\mathbf{A}=0, \mathbf{B}=1\}$ ;  $\{\mathbf{A}=1, \mathbf{B}=0\}$ ; and  $\{\mathbf{A}=1, \mathbf{B}=1\}$ . In the truth table, these are listed as follows:

#### Table 1.4 Truth Table for AND Gate

| Α | В | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Information Representation, Logic Gates, Boolean Algebra, Circuits, Registers and Counters

NOTES

In Table 1.4, F represents the output of two inputs in the AND gate with input signals A and B.

Symbol: F=A.B (where '.' implies AND operation)

The following figure represents the AND gate:

Fig. 1.4 ANDGate

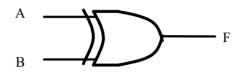

## 1.5.3 OR Gate

A basic OR gate is a two input, single output gate. Unlike the AND gate, the output is 1 when any one of the input signals is 1. The OR gate output is 0 only when both the inputs are 0. The truth table for the OR gate is as follows:

| Table 1.5 | Truth Table for ORG ate |

|-----------|-------------------------|

|           |                         |

|           |                         |

|           |                         |

|           |                         |

|           |                         |

|           |                         |

|           |                         |

|           |                         |

| А | В | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Symbol: F=A+B (where '+' implies OR operation)

The following figure represents OR gate:

Fig. 1.5 CRGate

# 1.5.4 XOR Gate

A gate related to the OR gate is the XOR gate or exclusive OR gate in which the output is 1 when one, and only one, of the inputs is 1. In other words, the XOR output is 1 if the inputs are different. The truth table for the XOR gate is as follows:

Self-Learning Material Information Representation, Logic Gales, Boolean Algebra, Circuits, Registers and Counters

NOTES

#### Table 1.6 Truth Table for XORGate

| Α | В | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

**Symbol:**  $F = A \oplus B$  (where ' $\oplus$ ' implies XOR operation)

The following figure represents XOR gate:

Fig. 1.6 XORGate

# **1.6 BOOLEAN ALGEBRA**

Basic logic functions and operations are the AND function (logical multiplication), the OR function (logical addition) and the NOT operation (logical complementation).

## **1.6.1 Logical AND Operation**

The logical AND operation between two Boolean variables, **A** and **B** is written as Y = A. **B** The common symbol for this operation is the multiplication sign (.). Table 1.7 shows that the result of logically ANDing the variables **A** and **B** is logical 0 for all cases except when both **A** and **B** are logical 1. Normally, the dot denoting the AND function is omitted and **A**. **B** is written as **AB**

# 1.6.2 Logical OR Operation

The logical OR operation between two Boolean variables, **A** and **B** is written as Y = A + B and can be represented by a truth table. Table 1.8 shows that the result of OR ing the variables **A** and **B** is logical 1 when either **A** or **B** (or both) are logical 1. The common symbol for logical addition is the plus sign (+).

| Table 1.7 Logical AND Operation |   |    | DOperation             | Table 1.8 Logical OROperation |   |                |  |

|---------------------------------|---|----|------------------------|-------------------------------|---|----------------|--|

|                                 | A | вч | <i>ί</i> = <b>Α. Β</b> | Α                             | В | <b>Y= A+ B</b> |  |

|                                 | 0 | 0  | 0                      | 0                             | 0 | 0              |  |

|                                 | 0 | 1  | 0                      | 0                             | 1 | 1              |  |

|                                 | 1 | 0  | 0                      | 1                             | 0 | 1              |  |

|                                 | 1 | 1  | 1                      | 1                             | 1 | 1              |  |

## **1.6.3** Logical Complementation (Inversion)

The logical inverse operation changes logical 1 to logical 0 and vice versa. It is also called the NOT operation. The common symbol for this operation is a bar

over the function or variable. Several notations are used to indicate the NOT operation, such as adding asterisks, stars, primes, etc., 'NOT **A**' or the 'Complement of **A**' will be written as  $\overline{\mathbf{A}}$  or **A**.

A Boolean function is an algebraic expression formed with binary variables, the logic operation symbols, parentheses and equal sign. A Boolean function can be transformed from an algebraic expression into a logic diagram composed of AND, OR, NOT (inverter) gates.

The purpose of Boolean algebra is to facilitate the analysis and design of digital circuits. It provides a convenient tool to:

- (i) Express in algebraic form a truth table relationship between variables.

- (iii) Express in algebraic form the input-output relationship of logic diagram.

- (**)** Find simpler circuits for the same function.

#### 1.6.4 Basic Laws of Boolean Algebra

Three logic functions (AND, OR and NOT or complement) provide the foundation for all digital systems analysis and design. Logic operations can be expressed and minimized mathematically using, laws and theorems of Boolean algebra. It is a convenient and systematic method of expressing and analysing the operation of digital circuits and systems. The following are the basic laws of Boolean algebra.

**Boolean addition:** The basic rules of Boolean addition are given as follows:

$$0 + 0 = 0$$

$0 + 1 = 1$

$1 + 0 = 1$

$1 + 1 = 1$

Boolean addition is same as the logical OR addition.

**Boolean Multiplication:** The basic rules of Boolean multiplication method are given as follows:

$$0.0 = 0$$

$0.1 = 0$

$1.0 = 0$

$1.1 = 1$

Boolean multiplication is same as the logical AND operation.

**Properties of Boolean Algebra:** Boolean algebra is a mathematical system consisting of a set of two or more distinct elements, two binary operators denoted by the symbols (+) and (.), and one unary operator denoted by the symbol either bar (-) or prime ('). This satisfies the commutative, associative, distributive, absorption, consensus and idempotency properties of the Boolean algebra.

Information Representation, Logic Gates, BooleanAlgebra, Circuits, Registers and Counters

NOTES

Information Representation, Logic Gates, Boolean/Algebra, Circuits, Registers and Counters

NOTES

Commutative Laws: Boolean addition is commutative and is given by,

$$\mathbf{A} + \mathbf{B} = \mathbf{B} + \mathbf{A} \qquad \dots (1.1)$$

These laws indicate that the order in which we OR or AND two variables is not important; the result is the same.

**Associative Laws:**

$$A+(B+C) = (A+B) + C$$

...(1.3)

These laws state that we can group the variables in an AND expression or OR expression any way we want.

**Distributive Laws:**

$$A+B.C=(A+B).(A+C)$$

These laws state that an expression can be expanded by multiplying term by term just the same as in ordinary algebra.

This theorem also indicates that you can factor an expression. That is, if you have a sum of two (or more) terms, each of which contains a common variable. The common variable can be factored out just as in ordinary algebra.

|        | $\mathbf{A} + (\mathbf{B}, \mathbf{C}) = (\mathbf{A} + \mathbf{B}) \cdot (\mathbf{A} + \mathbf{C})$ | <b>C</b> )(1.6)                                                                    |

|--------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Proof: | <b>A</b> + <b>B</b> . <b>C</b> = <b>A</b> . 1 + <b>B</b> . <b>C</b>                                 | (∵ <b>A</b> . 1 = <b>A</b> )                                                       |

|        | = <b>A</b> . (1 + <b>B</b> ) + <b>BC</b>                                                            | (∵ 1 + <b>B</b> = 1)                                                               |

|        | = <b>A</b> . 1 + <b>A</b> . <b>B</b> + <b>B</b> C                                                   | $(:: \mathbf{A}(\mathbf{B}+\mathbf{C})=\mathbf{A}\mathbf{B}+\mathbf{A}\mathbf{C})$ |

|        | = <b>A</b> . (1 + <b>C</b> ) + <b>AB</b> + <b>BC</b>                                                | (∵ 1 + <b>C</b> = 1)                                                               |

|        | = <b>A</b> . 1 + <b>AC</b> + <b>AB</b> + <b>BC</b>                                                  |                                                                                    |

|        | $= \mathbf{A}. \mathbf{A} + \mathbf{A}\mathbf{C} + \mathbf{A}\mathbf{B} + \mathbf{B}\mathbf{C}$     | (∵ <b>A</b> . <b>A</b> = <b>A</b> )                                                |

|        | = <b>A</b> ( <b>A</b> + <b>C</b> ) + <b>B</b> ( <b>A</b> + <b>C</b> )                               |                                                                                    |

|        | A+(B, C) = (A+B).(A+C)                                                                              |                                                                                    |

**Absorption Laws:**

...

(:::)

$\mathbf{A}.\ (\mathbf{A}+\mathbf{B})=\mathbf{A}$

$\mathbf{A} + \overline{\mathbf{A}} \cdot \mathbf{B} = \mathbf{A} + \mathbf{B}$

(i)

$$A + AB = A$$

...(1.7)

Proof:

$$A + AB = A$$

.  $1 + AB = A(1 + B)$

$\therefore A + AB = A$ .  $1 = A$

(ii)  $A$ .  $(A + B) = A$  ...(1.8)

Proof:  $A$ .  $(A + B) = A$ .  $A + A$ .  $B$

$= A + AB = A(1 + B) = A$ . 1

...(1.9)

Self - Learning 24 Material

| Proof: $\mathbf{A} + \overline{\mathbf{A}}$ . $\mathbf{B} = (\mathbf{A} + \overline{\mathbf{A}})(\mathbf{A} + \mathbf{B})$ [: $\mathbf{A} + \mathbf{B}\mathbf{C} = (\mathbf{A} + \mathbf{B}).(\mathbf{A} + \mathbf{C})$ ]                     |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| $= 1 \cdot (\mathbf{A} + \mathbf{B}) \qquad (\because \mathbf{A} + \overline{\mathbf{A}} = 1)$                                                                                                                                                | C |

| $\therefore \qquad \mathbf{A} + \overline{\mathbf{A}} \cdot \mathbf{B} = \mathbf{A} + \mathbf{B}$                                                                                                                                             |   |

| (iv) $A(\bar{A}+B) = AB$ (1.10)                                                                                                                                                                                                               |   |

| Proof: $\mathbf{A} (\overline{\mathbf{A}} + \mathbf{B}) = (\mathbf{A}\overline{\mathbf{A}}) + (\mathbf{A}\mathbf{B})$                                                                                                                         |   |

| $\therefore  \mathbf{A} \left( \overline{\mathbf{A}} + \mathbf{B} \right) = \mathbf{A} \mathbf{B} \qquad (\because \mathbf{A} \overline{\mathbf{A}} = 0)$                                                                                     |   |

| Consensus Laws:                                                                                                                                                                                                                               |   |

| (i) $AB+\overline{A}C+BC = AB+\overline{A}C$ (1.11)                                                                                                                                                                                           |   |

| Proof: $AB+\overline{AC}+BC = AB+\overline{AC}+BC.1$                                                                                                                                                                                          |   |

| $= \mathbf{A}\mathbf{B} + \overline{\mathbf{A}}\mathbf{C} + \mathbf{B}\mathbf{C}(\mathbf{A} + \overline{\mathbf{A}}) \qquad (\because \mathbf{A} + \overline{\mathbf{A}} = 1)$                                                                |   |

| $=$ <b>AB</b> + $\overline{\mathbf{A}}\mathbf{C}$ + $\mathbf{ABC}$ + $\overline{\mathbf{ABC}}$                                                                                                                                                |   |

| $=$ <b>AB</b> (1 + <b>C</b> ) + $\overline{\mathbf{AC}}(1 + \mathbf{B})$                                                                                                                                                                      |   |

| $\therefore \qquad \mathbf{AB} + \mathbf{\overline{AC}} + \mathbf{BC} = \mathbf{AB} + \mathbf{\overline{AC}} \qquad (\because 1 + \mathbf{C} = 1)$                                                                                            |   |

| (ii) $(A+B)(\overline{A}+C)(B+C) = (A+B)(\overline{A}+C)$ (1.12)                                                                                                                                                                              |   |

| Proof: $(\mathbf{A} + \mathbf{B})(\mathbf{\overline{A}} + \mathbf{C})(\mathbf{B} + \mathbf{C}) = (\mathbf{A} + \mathbf{B})(\mathbf{\overline{A}} + \mathbf{C})(\mathbf{B} + \mathbf{C} + 0)$                                                  |   |

| $= (\mathbf{A} + \mathbf{B})(\mathbf{\overline{A}} + \mathbf{C})(\mathbf{B} + \mathbf{C} + \mathbf{A}\mathbf{\overline{A}})$                                                                                                                  |   |

| $= (\mathbf{A} + \mathbf{B})(\mathbf{\overline{A}} + \mathbf{C})(\mathbf{B} + \mathbf{C} + \mathbf{A})(\mathbf{B} + \mathbf{C} + \mathbf{\overline{A}})$                                                                                      |   |

| [:: <b>A+ BC</b> = ( <b>A+ B</b> )( <b>A+ C</b> )]                                                                                                                                                                                            |   |

| $= (\mathbf{A} + \mathbf{B})(\mathbf{A} + \mathbf{B} + \mathbf{C})(\mathbf{\overline{A}} + \mathbf{C})(\mathbf{\overline{A}} + \mathbf{C} + \mathbf{B})$                                                                                      |   |

| $\therefore \qquad (\mathbf{A} + \mathbf{B})(\mathbf{\overline{A}} + \mathbf{C})(\mathbf{B} + \mathbf{C}) = (\mathbf{A} + \mathbf{B})(\mathbf{\overline{A}} + \mathbf{C}) \qquad [\because \mathbf{A}(\mathbf{A} + \mathbf{B}) = \mathbf{A}]$ |   |

| The other basic laws of Boolean algebra are given in Table 1.9.                                                                                                                                                                               |   |

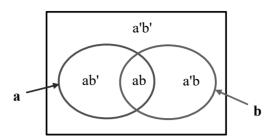

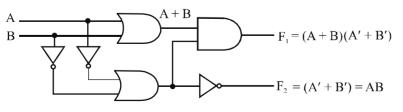

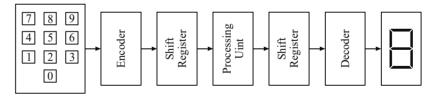

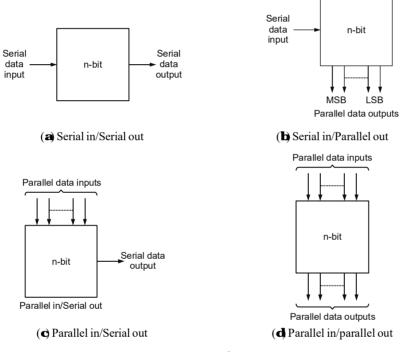

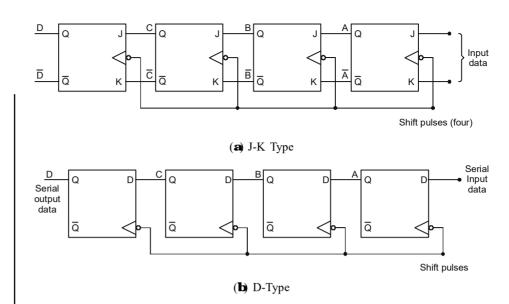

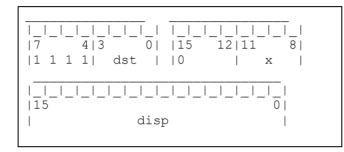

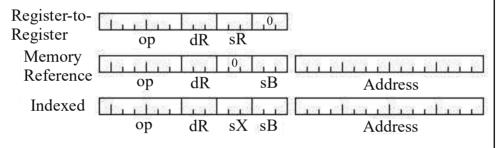

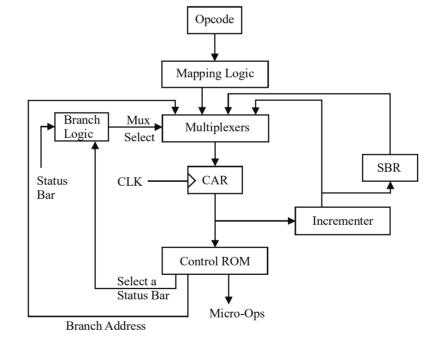

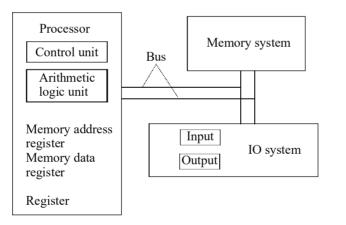

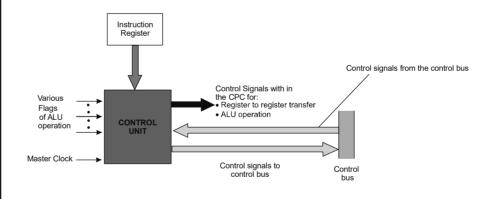

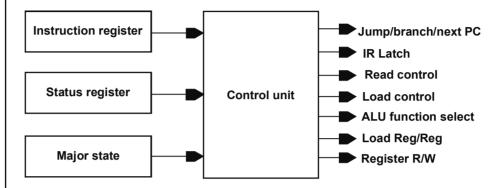

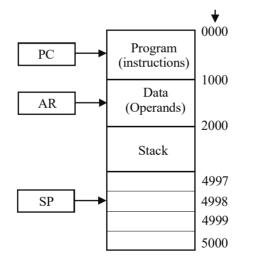

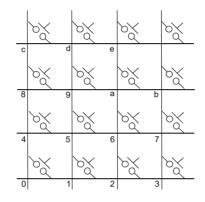

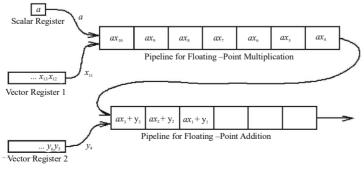

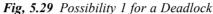

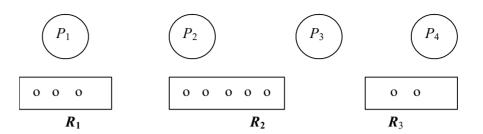

Truth Table 1.9 Laws of Bodean Algebra